1 MORRISON & FOERSTER LLP KARL J. KRAMER (Bar No. 136433) 2 KKramer@mofo.com DIANA LUO (Bar No. 233712) 3 dluo@mofo.com 755 Page Mill Road FIED 4 Palo Alto, CA 94304-1018 Telephone: (650) 813-5600 5 Facsimile (650) 494-0792 DEC 23 2010 Attorneys for Plaintiff

ALTERA CORPORATION 6 E. CLERK, U.S. METRICT COURT NORTHERN DISTRICT OF CALIFORNIA 7 8 UNITED STATES DISTRICT COURT 9 NORTHERN DISTRICT OF CALIFORNIA 10 CV10-0586611 ALTERA CORPORATION Case No. 12 Plaintiff, COMPLAINT FOR PATENT 13 INFRINGEMENT 14 v. **DEMAND FOR JURY TRIAL** 15 INTELLITECH CORPORATION 16 Defendant. 17 18 19 20 21 22 23 24 25 26 27 COMPLAINT FOR PATENT INFRINGEMENT AND DEMAND FOR JURY TRIAL 28 CASE NO sf-2912349

| 1  | Plaintiff Aftera Corporation ("Aftera"), by and through its attorneys, affeges as follows:           |  |  |

|----|------------------------------------------------------------------------------------------------------|--|--|

| 2  | <u>PARTIES</u>                                                                                       |  |  |

| 3  | 1. Altera is a corporation organized under the laws of the State of Delaware with its                |  |  |

| 4  | principal place of business at 101 Innovation Drive, San Jose, California 95134. Altera regularly    |  |  |

| 5  | conducts business in the Northern District of California.                                            |  |  |

| 6  | 2. Upon information and belief, Defendant Intellitech Corporation ("Intellitech") is a               |  |  |

| 7  | corporation organized under the laws of the State of New Hampshire with its principal place of       |  |  |

| 8  | business at 69 Venture Drive, Dover, New Hampshire 03820. Intellitech regularly conducts             |  |  |

| 9  | business in the Northern District of California.                                                     |  |  |

| 10 | JURISDICTION AND VENUE                                                                               |  |  |

| 11 | 3. This is an action for patent infringement arising under the patent laws of the United             |  |  |

| 12 | States, Title 35 of the United States Code. Jurisdiction as to these claims is conferred on this     |  |  |

| 13 | Court by 28 U.S.C. §§ 1331 and 1338(a).                                                              |  |  |

| 14 | 4. Upon information and belief, this Court has personal jurisdiction over Intellitech                |  |  |

| 15 | because Intellitech has sufficient contacts with this judicial district and Intellitech regularly    |  |  |

| 16 | conducts business within this judicial district. Upon information and belief, Intellitech directly   |  |  |

| 17 | distributes, offers for sale or license, sells or licenses, and advertises its products and services |  |  |

| 18 | within the State of California and this judicial district.                                           |  |  |

| 19 | 5. Venue is proper in this judicial district under 28 U.S.C. §§ 1391 and 1400(b).                    |  |  |

| 20 | Intellitech is a corporation that is subject to personal jurisdiction in this district.              |  |  |

| 21 | INTRADISTRICT ASSIGNMENT                                                                             |  |  |

| 22 | 6. This is an Intellectual Property Action to be assigned on a district-wide basis                   |  |  |

| 23 | pursuant to Civil Local Rule 3-2(c).                                                                 |  |  |

| 24 | BACKGROUND                                                                                           |  |  |

| 25 | 7. Altera is a preeminent supplier of programmable logic solutions, offering Field                   |  |  |

| 26 | Programmable Gate Arrays ("FPGAs"), Complex Programmable Logic Devices ("CPLDs"), and                |  |  |

| 27 | COMPLAINT FOR PATENT INFRINGEMENT AND DEMAND FOR JURY TRIAL                                          |  |  |

| 28 | COMPLAINT FOR PATENT INFRINGEMENT AND DEMAND FOR JURY TRIAL  CASE NO.  1                             |  |  |

|    | sf-2912349                                                                                           |  |  |

| 2  |

|----|

| 3  |

| 4  |

| 5  |

| 6  |

| 7  |

| 8  |

| 9  |

| 10 |

| 11 |

| 12 |

| 13 |

| 14 |

| 15 |

| 16 |

| 17 |

| 18 |

| 19 |

| 20 |

| 21 |

| 22 |

| 23 |

| 24 |

| 25 |

| 26 |

| 27 |

Application-Specific Integrated Circuit ("ASICs") in combination with software tools, intellectual property, and support to customers world-wide.

- 8. The pioneering work of Altera's scientists and engineers has been rewarded with many United States Patents, including the following: 6,421,812 ("the '812 Patent"), 5,563,592 ("the '592 Patent"), and 7,036,046 ("the '046 Patent").

- 9. Each of the inventors of the Altera patents assigned their patents to Altera, so that Altera is and at all times has been the sole owner of all right and title to the patents, including the right to recover damages for past and current infringement.

- 10. Intellitech develops and licenses integrated circuits ("ICs"), Intellectual Property ("IP"), and software for configuration, debug and test of electronic products including System-on-a-Chip, ICs, print circuit boards ("PCB") and electronic systems. Intellitech's products include the SystemBIST product for configuring, programming, and testing memories, PLDs and other programmable devices; the Eclipse software for developing and validating system configurations and tests; the Fast Access Controller ("FAC") product for use with 1149.1 test infrastructures to enable in-system programming of FLASH memory devices; and the NEBULA Silicon Debugger for debugging and validation of ICs. Primary end users of these products include electronic product manufacturers and the semiconductor industry.

#### **COUNT I**

### (Infringement of the '812 Patent)

- 11. Altera hereby restates and realleges the allegations set forth in paragraphs 1 through 10 above and incorporates them by reference.

- 12. On July 16, 2002, the '812 Patent entitled "Programming mode selection with JTAG circuits" was duly and legally issued to Altera by the United States Patent and Trademark Office. Altera is the owner of the entire right, title, and interest in and to the '812 Patent. A true and correct copy of the '812 Patent is attached as Exhibit A to this Complaint.

COMPLAINT FOR PATENT INFRINGEMENT AND DEMAND FOR JURY TRIAL CASE NO.

28

- 13. Altera has not licensed or otherwise authorized Intellitech to make, use, offer for sale or sell any products that embody the inventions of the '812 Patent.

- 14. Intellitech has directly infringed and continues to directly infringe the '812 Patent by its unlicensed use of methods that embody the invention claimed by the '812 Patent in the United States during development, prototyping, testing, verification, and demonstration of its SystemBIST and FAC products with the Eclipse Software.

- Intellitech has had actual knowledge of the '812 Patent since at least November 4,

2010.

- 16. Intellitech has indirectly infringed and continues to indirectly infringe the '812 Patent by inducing end users to infringe the '812 Patent by using the SystemBIST and FAC products with Eclipse Software. Intellitech intentionally took action that induced end users to infringe the '812 Patent by marketing, selling, and supporting the SystemBIST and FAC products and Eclipse Software. Intellitech had awareness of the '812 Patent in circumstances in which it knew or should have known that its actions would cause direct infringement by end users.

- 17. Intellitech has indirectly infringed and continues to indirectly infringe the '812 Patent by contributing to direct infringement by end users who use the SystemBIST and FAC products with Eclipse Software. Intellitech supplied an important component of the infringing part of the method, the component is not a common component suitable for non-infringing use, and Intellitech supplied the component with the knowledge of the '812 Patent and knowledge that the component was especially made or adapted for use in an infringing manner.

- 18. Upon information and belief, Intellitech's infringement of Altera's '812 Patent has been and will continue to be willful, wanton and deliberate.

- 19. Altera is damaged and irreparably injured by Intellitech's infringing activities and will continue to be so damaged and irreparably injured unless Intellitech's infringing activities are enjoined by this Court.

COMPLAINT FOR PATENT INFRINGEMENT AND DEMAND FOR JURY TRIAL CASE NO.

| 1  | 20. Intellitech is thus liable to Altera for infringement of the '812 Patent pursuant to 35           |  |  |  |  |

|----|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| 2  | U.S.C. § 271.                                                                                         |  |  |  |  |

| 3  | <u>COUNT II</u>                                                                                       |  |  |  |  |

| 4  | (Infringement of the '592 Patent)                                                                     |  |  |  |  |

| 5  | 21. Altera hereby restates and realleges the allegations set forth in paragraphs 1 through            |  |  |  |  |

| 6  | 20 above and incorporates them by reference.                                                          |  |  |  |  |

| 7  | 22. On October 8, 1996, the '592 Patent entitled "Programmable logic device having a                  |  |  |  |  |

| 8  | compressed configuration file and associated decompression" was duly and legally issued to            |  |  |  |  |

| 9  | Altera by the United States Patent and Trademark Office. Altera is the owner of the entire right,     |  |  |  |  |

| 10 | title, and interest in and to the '592 Patent. A true and correct copy of the '592 Patent is attached |  |  |  |  |

| 11 | as Exhibit B to this Complaint.                                                                       |  |  |  |  |

| 12 | 23. Altera has not licensed or otherwise authorized Intellitech to make, use, offer for               |  |  |  |  |

| 13 | sale or sell any products that embody the inventions of the '592 Patent.                              |  |  |  |  |

| 14 | 24. Intellitech has directly infringed and continues to directly infringe the '592 Patent             |  |  |  |  |

| 15 | by its unlicensed use of methods that embody the invention claimed by the '592 Patent in the          |  |  |  |  |

| 16 | United States during development, prototyping, testing, verification, and demonstration of the        |  |  |  |  |

| 17 | SystemBIST product with Eclipse Software to program FLASH devices.                                    |  |  |  |  |

| 18 | 25. Intellitech has had actual knowledge of the '592 Patent since at least November 4,                |  |  |  |  |

| 19 | 2010.                                                                                                 |  |  |  |  |

| 20 | 26. Intellitech has indirectly infringed and continues to indirectly infringe the '592                |  |  |  |  |

| 21 | Patent by inducing end users to directly infringe the '592 Patent by using the SystemBIST and         |  |  |  |  |

| 22 | FAC products with Eclipse Software. Intellitech intentionally took action that induced end users      |  |  |  |  |

| 23 | to infringe the '592 Patent by marketing, selling, and supporting the SystemBIST and FAC              |  |  |  |  |

| 24 | products. Intellitech had awareness of the '592 Patent in circumstances in which it knew or           |  |  |  |  |

| 25 | should have known that its actions would cause direct infringement by end users.                      |  |  |  |  |

| 26 |                                                                                                       |  |  |  |  |

| 27 | COMPLAINT FOR PATENT INFRINGEMENT AND DEMAND FOR JURY TRIAL                                           |  |  |  |  |

| 28 | CASE NO.  4                                                                                           |  |  |  |  |

|    | sf-2912349                                                                                            |  |  |  |  |

,

| 1  |

|----|

| 2  |

| 3  |

| 4  |

| 5  |

| 6  |

| 7  |

| 8  |

| 9  |

| 10 |

| 11 |

| 12 |

| 13 |

| 14 |

| 15 |

| 16 |

| 17 |

| 18 |

| 19 |

| 20 |

| 21 |

| 22 |

| 23 |

| 24 |

| 25 |

| 26 |

| 27 |

| 28 |

- 27. Intellitech has indirectly infringed and continues to indirectly infringe the '592 Patent by contributing to direct infringement by end users who use the SystemBIST and FAC products. Intellitech supplied an important component of the infringing part of the method, the component is not a common component suitable for non-infringing use, and Intellitech supplied the component with the knowledge of the '592 Patent and knowledge that the component was especially made or adapted for use in an infringing manner.

- 28. Upon information and belief, Intellitech's infringement of Altera's '592 Patent has been and will continue to be willful, wanton and deliberate.

- 29. Altera is damaged and irreparably injured by Intellitech's infringing activities and will continue to be so damaged and irreparably injured unless Intellitech's infringing activities are enjoined by this Court.

- 30. Intellitech is thus liable to Altera for infringement of the '592 Patent pursuant to 35 U.S.C. § 271.

### **COUNT III**

# (Infringement of the '046 Patent)

- 31. Altera hereby restates and realleges the allegations set forth in paragraphs 1 through 50 above and incorporates them by reference.

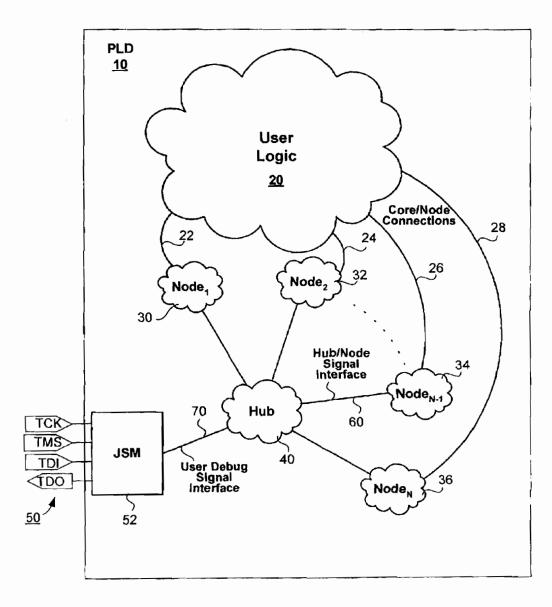

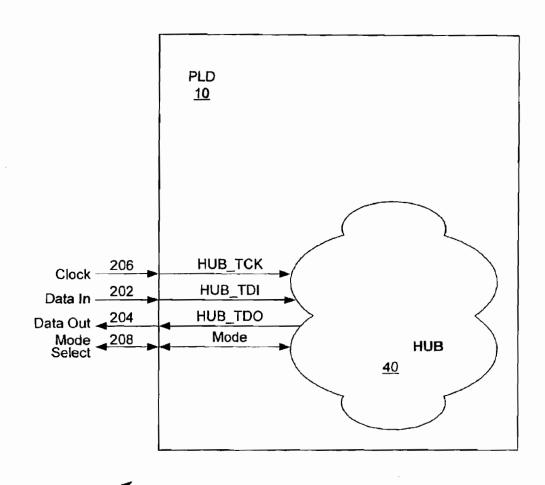

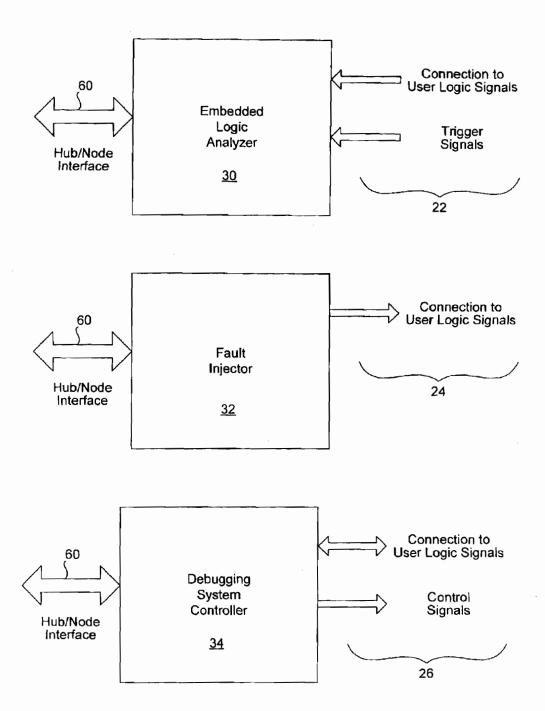

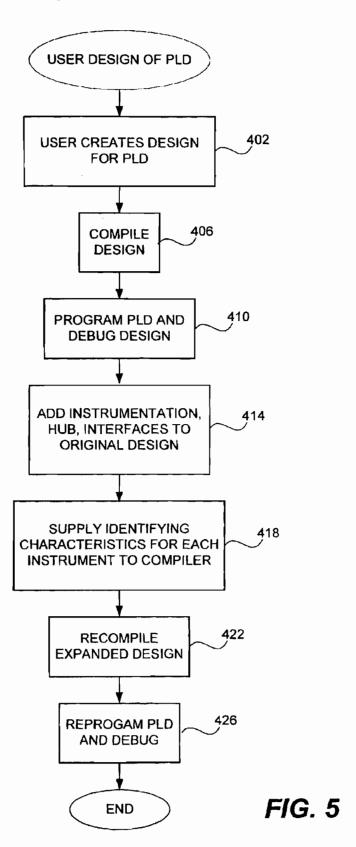

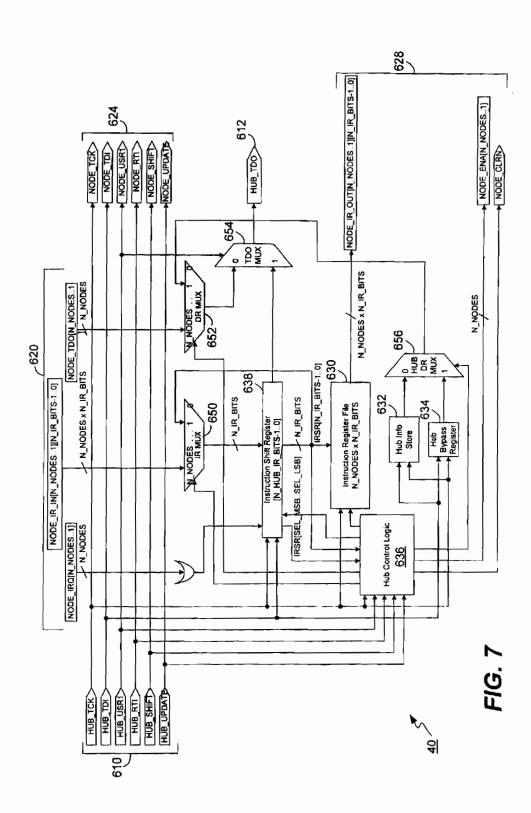

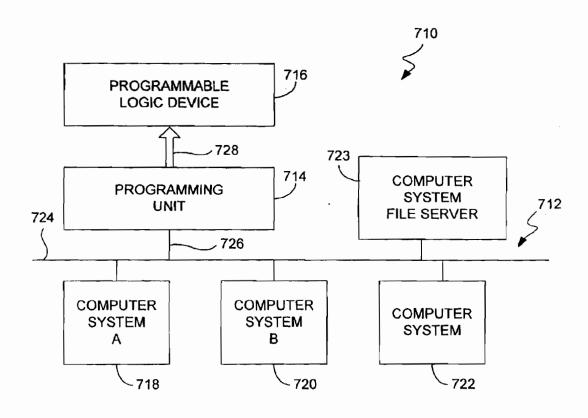

- 32. On April 25, 2006, the '046 Patent entitled "PLD debugging hub" was duly and legally issued to Altera by the United States Patent and Trademark Office. Altera is the owner of the entire right, title, and interest in and to the '046 Patent. A true and correct copy of the '046 Patent is attached as Exhibit C to this Complaint.

- 33. Altera has not licensed or otherwise authorized Intellitech to make, use, offer for sale or sell any products that embody the inventions of the '046 Patent.

- 34. Intellitech has directly infringed and continues to directly infringe the '046 Patent by its unlicensed use of systems that embody the invention claimed by the '046 Patent in the

COMPLAINT FOR PATENT INFRINGEMENT AND DEMAND FOR JURY TRIAL CASE NO.

sf-2912349

| 1  | in this litigation;                                                                              |                                                                                        |  |  |

|----|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|

| 2  | В.                                                                                               | An order permanently enjoining Intellitech, its officers, agents, servants,            |  |  |

| 3  | employees, attorneys and affiliated companies, its assigns and successors in interest, and those |                                                                                        |  |  |

| 4  | persons in ac                                                                                    | ctive concert or participation with it, from continued acts of infringement of the     |  |  |

| 5  | patents at iss                                                                                   | sue in this litigation;                                                                |  |  |

| 6  | D.                                                                                               | An order awarding Altera statutory damages and damages according to proof              |  |  |

| 7  | resulting from                                                                                   | m Intellitech's infringement of the patents at issue in this litigation, together with |  |  |

| 8  | prejudgment                                                                                      | and post-judgment interest;                                                            |  |  |

| 9  | E.                                                                                               | Trebling of damages under 35 U.S.C. § 284 in view of the willful and deliberate        |  |  |

| 10 | nature of Inte                                                                                   | ellitech's infringement of the patents at issue in this litigation;                    |  |  |

| 11 | F.                                                                                               | An order awarding Altera its costs and attorney's fees under 35 U.S.C. § 285; and      |  |  |

| 12 | G.                                                                                               | Any and all other legal and equitable relief as may be available under law and         |  |  |

| 13 | which the co                                                                                     | urt may deem proper.                                                                   |  |  |

| 14 | Dated: Dece                                                                                      | ember 23, 2010 KARL J. KRAMER                                                          |  |  |

| 15 |                                                                                                  | DIANA LUO<br>MORRISON & FOERS/TEK LLP                                                  |  |  |

| 16 |                                                                                                  | By: // // //                                                                           |  |  |

| 17 |                                                                                                  | KARL J. KRAMER                                                                         |  |  |

| 18 |                                                                                                  | Attorneys for Plaintiff ALTERA CORPORATION                                             |  |  |

| 19 |                                                                                                  | ALIBRAT COIL ORATION                                                                   |  |  |

| 20 |                                                                                                  |                                                                                        |  |  |

| 21 |                                                                                                  |                                                                                        |  |  |

| 22 |                                                                                                  |                                                                                        |  |  |

| 23 |                                                                                                  |                                                                                        |  |  |

| 24 |                                                                                                  |                                                                                        |  |  |

| 25 |                                                                                                  |                                                                                        |  |  |

| 26 |                                                                                                  |                                                                                        |  |  |

| 27 | COMPLAINT FO                                                                                     | OR PATENT INFRINGEMENT AND DEMAND FOR JURY TRIAL                                       |  |  |

| 28 | CASE NO.                                                                                         | <b>7</b>                                                                               |  |  |

sf-2912349

sf-2912349

# **DEMAND FOR A JURY TRIAL**

Plaintiff hereby demands a jury trial on all issues so triable under the laws as provide by Rule 38(b) of the Federal Rules of Civil Procedure.

Dated: December 23, 2010

KARL J. KRAMER

DIANA LUO

MORRISON & FOERSTER LLP

Attorneys for Plaintiff

ALTERA CORPORATION

COMPLAINT FOR PATENT INFRINGEMENT AND DEMAND FOR JURY TRIAL CASE NO.

# Exhibit A

# (12) United States Patent Wang et al.

(10) Patent No.:

US 6,421,812 B1

(45) Date of Patent:

Jul. 16, 2002

# (54) PROGRAMMING MODE SELECTION WITH JTAG CIRCUITS

(75) Inventors: Xiaobao Wang, Santa Clara; Chiakang

Sung, Milpitas; Joseph Huang, San Jose; Bonnle Wang, Cupertino; Khal Nguyen, San Jose; Richard G. Cliff,

Milpitas, all of CA (US)

(73) Assignee: Altera Corporation, San Jose, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 09/094,186

(22) Filed: Jun. 9, 1998

Related U.S. Application Data

(60) Provisional application No. 60/049,478, filed on Jun. 13, 1997, provisional application No. 60/050,953, filed on Jun. 13, 1997, provisional application No. 60/049,275, filed on Jun. 10, 1997, provisional application No. 60/049,246, filed on Jun. 10, 1997, provisional application No. 60/052,990, filed on Jun. 10, 1997, provisional application No. 60/049, 247, filed on Jun. 10, 1997, provisional application No. 60/049,243, filed on Jun. 10, 1997, and provisional application No. 60/049,245, filed on Jun. 10, 1997.

| (51) | Int. Cl. <sup>7</sup> | G06F 17/50              |

|------|-----------------------|-------------------------|

| (52) | U.S. Cl               | 716/5                   |

| (58) | Field of Search       | . 716/5; 711/5; 714/727 |

U.S. PATENT DOCUMENTS

### (56) References Cited

| 3,761,695 A | 9/1973  | Eichelberger 235/153 AC      |

|-------------|---------|------------------------------|

| 3,783,254 A | 1/1974  | Eichelberger 235/152         |

| 3,806,891 A | 4/1974  | Eichelberger et al 340/172.5 |

| 4 488 259 A | 12/1984 | Mercy 364/900                |

| 4,667,325 A | 5/1987  | Kitano et al 371/25         |

|-------------|---------|-----------------------------|

| 4,701,920 A | 10/1987 | Resnick et al 371/25        |

| 5,175,859 A | 12/1992 | Miller et al 395/800        |

| 5,336,951 A | 8/1994  | Josephson et al 307/465     |

| 5,355,369 A | 10/1994 | Greenbergerl et al 371/22.3 |

(List continued on next page.)

#### FOREIGN PATENT DOCUMENTS

| EP | 0 639 006 A1 | 2/1995 |             |

|----|--------------|--------|-------------|

| EP | 0 828 163 A1 | 3/1998 |             |

| WO | WO 97/06599  | 2/1997 | H03K/19/177 |

#### OTHER PUBLICATIONS

Altera Corporation, Data Sheet, "Flex 10K Embedded Programmable Logic Family," Jul., 1995, ver. 1, pp. 1-39.

(List continued on next page.)

Primary Examiner—Matthew Smith

Assistant Examiner—Leigh Garbowski

(74) Attorney, Agent, or Firm—Townsend and Townsend

and Crew LLP

#### (57) ABSTRACT

A technique to provide higher system performance by increasing amount of data that may be transferred in parallel is to increase the number of external pins available for the input and output of user data (user I/O). Specifically, a technique is to reduce the number of dedicated pins used for user I/O, leaving more external pins available for user I/O. The dedicated pins used to implement a function such as the JTAG boundary scan architecture may be also be used to provide other functionality, such as to select the programming modes. In a specific embodiment, a JTAG instruction code that is not already used for a JTAG boundary scan instruction stored in an instruction register (220) may be used to replace the programming mode select pins (252) in a programmable logic device (PLD).

#### 29 Claims, 8 Drawing Sheets

#### U.S. PATENT DOCUMENTS

| 5,361,373 | Α | 11/1994   | Gilson 395/800          |

|-----------|---|-----------|-------------------------|

| 5,489,858 | Α | 2/1996    | Pierce et al 326/56     |

| 5,491,666 | Α | 2/1996    | Sturges 365/201         |

| 5,581,564 | Α | 12/1996   | Miller et al 371/22.3   |

| 5,590,305 | Α | 12/1996   | Terrill et al 395/430   |

| 5,594,367 | Α | 1/1997    | Trimberger et al 326/41 |

| 5,644,496 | Α | 7/1997    | Agrawal et al 364/489   |

| 5,650,734 | Α | 7/1997    | Chu et al 326/38        |

| 5,734,868 | Α | 3/1998    | Curd et al 395/500      |

| 5,737,567 | Α | 4/1998    | Whittaker et al 395/430 |

| 5,829,007 | Α | * 10/1998 | Wise et al 711/5        |

| 5,841,867 | Α | 11/1998   | Jacobson et al 380/25   |

| 5,869,979 | Α | 2/1999    | Bocchino 326/38         |

| 5,991,908 | Α | * 11/1999 | Baxter et al 714/727    |

| 6,058,255 | A | * 5/2000  | Jordan 716/5            |

| ,         |   |           |                         |

#### OTHER PUBLICATIONS

Altera Corporation, Data Sheet, "Flex 8000 Programmable Logic Device Family," Aug., 1994, ver. 4, pp. 1–22. Altera Corporation, Data Sheet, "Max 7000 Programmable Logic Device Family," Jun. 1996, ver 4, pp. 193–261. Altera Corporation, Application Note 39, "JTAG Boundary-ScanTesting In Altera Devices," Nov., 1995, ver. 3, pp. 1–28. IEEE Computer Society, "IEEE Standard Test Access Port and Boundary-Scan Architecture (IEEE Std 1149.1–1990)," Institute of Electrical and Electronics Engineers, Inc., New York, NY, Oct. 21, 1993, pp. 1–1 to 12–6 and Appendix A–1 to A–12.

IEEE Computer Society, "Supplement to (IEEE Std 1149.1–1990), IEEE Standard Test Access Port and Boudary-Scan Architecture (IEEE Std 11493.1b–1994)," Institute of Electrical and Electronics Engineers, Inc., New York, NY, Mar. 1, 1995, pp. 1–67.

Xilnix Corporation, "The Programmable Logic Data Book," 1993, pp. 1-1 to 10-8.

Xilnix Corporation, "The Programmable Logic Data Book," Section 9, 1994, pp. 9-1 to 9-32.

Xilnix Corporation, "The Programmable Logic Data Book," Product Description, "XC2000 Logic Cell Array Families," Aug. 1994, pp. 2–187 to 2–216.

Xilnix Corporation, "The Programmable Logic Data Book," Product Description, "XC3000, XC3000A, XC000L, SC3100, XC3100A Logic Cell Array Families," pp. 2–105 to 2–152.

Xilnix Corporation, "The Programmable Logic Data Book," Product Specification, "XC4000 Series Field Programmable Gate Arrays," Jul. 30, 1996, version 1.03, pp. 4-5 to 4-76.

<sup>\*</sup> cited by examiner

FIGURE 1

FIGURE 5

;

# PROGRAMMING MODE SELECTION WITH JTAG CIRCUITS

This application claims the benefit of a U.S. provisional application No. 60/049,275, filed Jun. 10, 1997; No. 60/049, 5 478, filed Jun. 13, 1997; No. 60/049,246, filed Jun. 10, 1997; No. 60/052,990, filed Jun. 10, 1997; No. 60/049,247, filed Jun. 10, 1997; No. 60/050,953, filed Jun. 13, 1997; and No. 60/049,245, filed Jun. 10, 1997, all of which are incorporated herein by 10 reference.

#### BACKGROUND OF THE INVENTION

The present invention relates to the field of integrated circuits, and more specifically to techniques to effectively provide greater number of external pins for input and output of data.

Semiconductor technology continues to improve. This technology allows greater and greater functionality to be provided by a single integrated circuit or "chip." Signals are input to and output from the chip using external pins or pads. The chip interfaces to external circuitry, possibly on other chips, using the external pins.

The performance of a system depends in part on the amount or rate at which data can be transferred on and off the chip. This transfer rate may be referred to as the data bandwidth. One technique for increasing system performance is to provide more rapid transfer rates. This may be accomplished by improvements in process technology or circuit design. Another technique to increase system performance is to transfer a greater amount of data at one time (or "in parallel"). Therefore, for greater performance, it is important there are many external pins available for input and output of user data.

In an integrated circuit, certain pins are sometimes dedicated to functions other than user data I/O. For example, in a programmable integrated circuit such as a PLD or FPGA, some pins may be dedicated to the programming and testing (such as JTAG boundary scan testing) of the device. These dedicated external pins reduce the number of pins available for user I/O. The performance of the chip may be detrimentally affected since not as many user I/O signals may be transferred in parallel.

Consequently, there is a need for techniques of effectively 45 providing greater number of external pins for input and output to obtain higher performance. Specifically, there is a need for techniques to reduce the number of external pins dedicated to functions other than user I/O, which would make a greater number of external pins available for the 50 input and output of user data.

#### SUMMARY OF THE INVENTION

The present invention is a technique to provide higher system performance by increasing the amount of data that may be transferred in parallel by increasing the number of external pins available for the input and output of user data (user I/O). One technique is to reduce the number of dedicated pins used for functions other than user I/O, leaving more external pins available for user I/O. The dedicated pins used to implement a function such as the JTAG boundary scan architecture may be also be used to provide other functionality, such as to select the programming modes. In a specific embodiment, a JTAG instruction code that is not already used for a JTAG boundary scan instruction may be used to replace the programming mode select pins in a programmable logic device (PLD).

In a technique of the present invention, the JTAG instruction used to replace the mode pins is shifted into a JTAG instruction register as are regular JTAG instructions. A JTAG boundary scan control logic block generates control signals to a programming mode decoder. Based on the instruction, the programming mode decoder selects the proper programming mode, and generates the appropriate programming mode signals. The programming mode signals are provided to the programming circuitry, and integrated circuit will be appropriately configured.

In a specific implementation, each single bit of the JTAG instruction code may be used to replace one programming mode select pin. In another implementation, the whole JTAG instruction code may be used to replace one mode select pin after instruction decoding. Technically, by doing this, many, or all, the mode pins can be eliminated, thus increasing the number of total available I/O pins. This concept provides advantages compared to JTAG programming and in-system programming (ISP) in such a way that a PLD device may be configured for different modes including test, scan, and programming modes.

The advantages of using JTAG instructions to replace programming the mode select pins of a programmable integrated circuit include saving device package costs and leaving space for more user I/Os. Overall, this increases the available functionality and value of the devices. There is relatively little cost to implement the circuits to implement PLD programming mode selection with JTAG circuits.

In a specific embodiment, the present invention is a method of configuring a programmable integrated circuit. An instruction is provided to a JTAG instruction register. The instruction is passed to a JTAG boundary scan control logic block. The JTAG boundary scan control logic block generates a control signal. The control signal is passed to a programming mode decoder. Based on the control signal, a programming mode signal is generated to place the programmable integrated circuit in a configuration mode.

Further, the present invention is a programmable integrated circuit including a JTAG state machine; an instruction register coupled to the JTAG state machine; a JTAG boundary scan control logic block coupled to the instruction register; and a programming mode decoder coupled to receive a mode signal from the JTAG boundary scan control logic block.

Another aspect of the present invention includes the use of JTAG circuitry resident on a programmable integrated circuit to select a programming mode of the integrated circuit. Further, the present invention includes the use of an instruction input to a JTAG instruction register, where this struction is not used to perform a IEEE 1149.1 standard function, to place a programmable integrated circuit into a specific programming mode identified by the instruction. A still further aspect of the present invention is the use of JTAG circuits on a programmable logic device to place the programmable logic device in a configuration mode.

Other objects, features, and advantages of the present invention will become apparent upon consideration of the following detailed description and the accompanying drawings, in which like reference designations represent like features throughout the figures.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 shows a digital system incorporating a programmable logic device;

FIG. 2 shows an implementation of programming mode selection using JTAG circuitry;

FIG. 3 shows an implementation of JTAG boundary scan control logic circuitry;

FIG. 4 shows an implementation of a programming mode decoder;

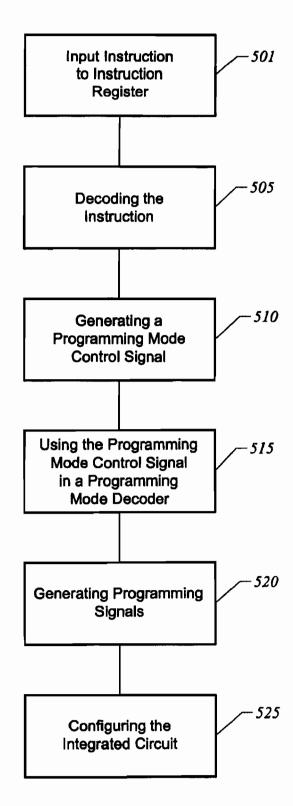

FIG. 5 shows a flow diagram of a technique for configuring an integrated circuit;

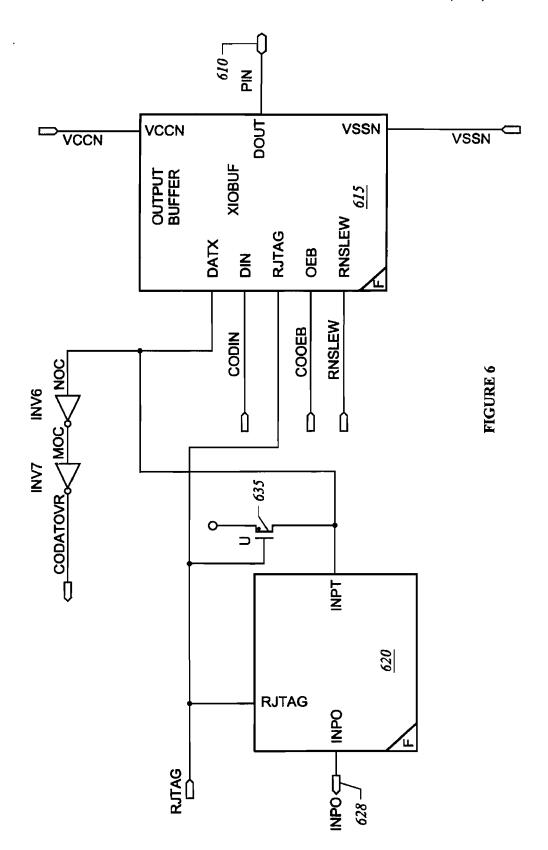

FIG. 6 shows circuitry for selectably enabling use of a JTAG input pin;

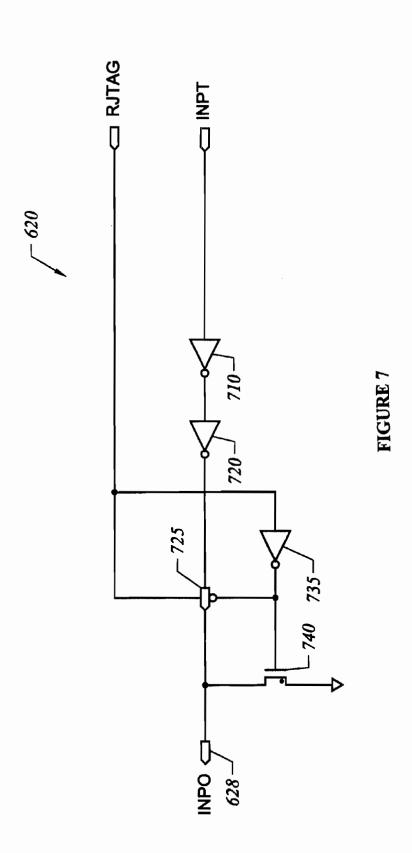

FIG. 7 shows a circuit implementation of a JTAG input buffer; and

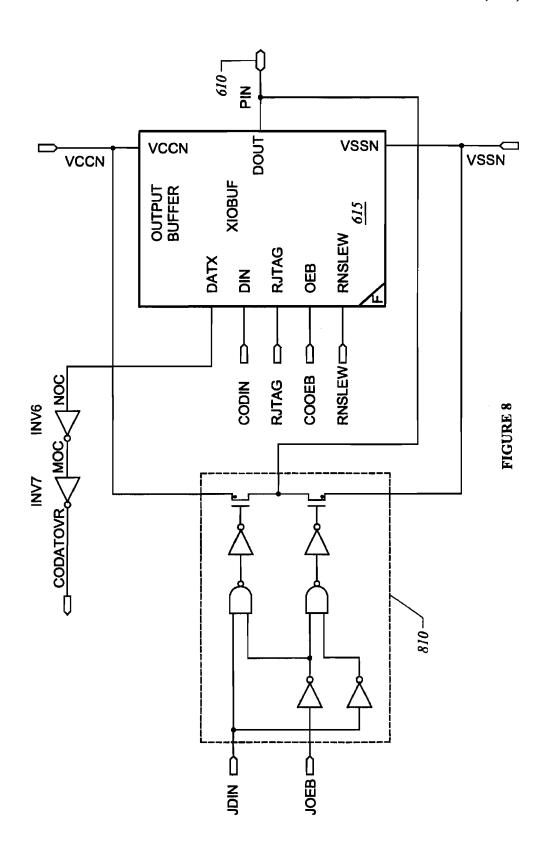

FIG. 8 shows a circuit implementation for selectably enabling use of a JTAG output pin.

# DESCRIPTION OF THE SPECIFIC EMBODIMENTS

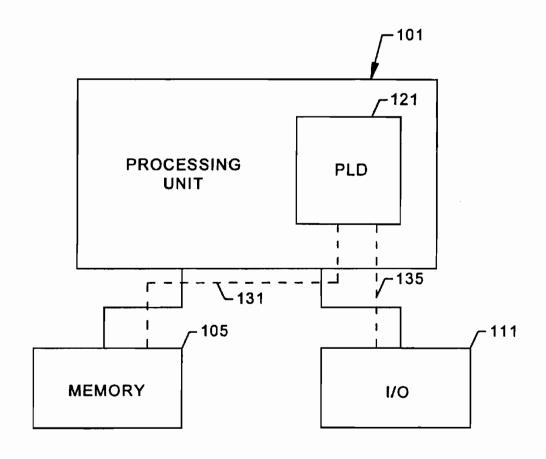

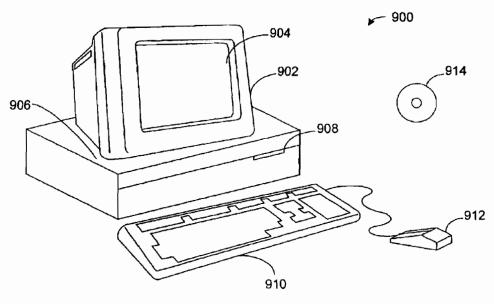

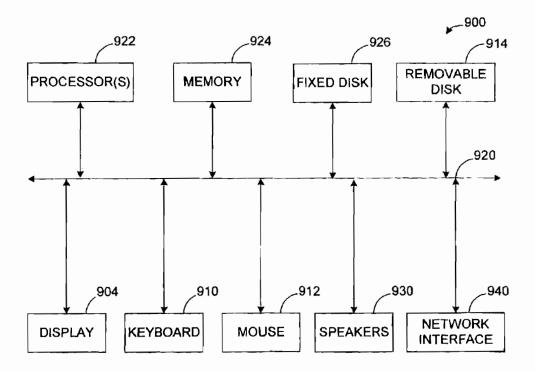

FIG. 1 shows a block diagram of a digital system. The system may be provided on a single board, on multiple boards, or even within multiple enclosures linked by electrical conductors or a network (e.g., a local area network or the internet). This digital system may be used in a wide variety of applications and industries including networking, telecommunications, automotive, control systems, consumer electronics, computers, workstations, military, industrial, digital processing, and many others. In the embodiment of FIG. 1, a processing unit 101 is coupled to a memory 105 and an I/O 111. Further, a programmable logic device (PLD) 121 is incorporated within this digital system. PLD 121 may be specially coupled to memory 105 through connection 131 and to I/O 111 through connection 135.

Programmable logic devices (PLDs) are sometimes also 30 referred to as PALs, PLAs, FPLAS, CPLDs, EPLDs, EEPLDs, LCAs, or FPGAs. PLDs are well-known integrated circuits that provide the advantages of fixed integrated circuits with the flexibility of custom integrated circuits. Such devices allow a user to electrically program 35 standard, off-the-shelf logic elements to meet a user's specific needs. See, for example, U.S. Pat. No. 4,617,479, incorporated herein by reference for all purposes. Such devices are currently represented by, for example, Altera's MAX® and FLEX® series of devices. The former are 40 described in, for example, U.S. Pat. Nos. 5,241,224 and 4,871,930, and the Altera Data Book, June 1996, all incorporated herein by reference in their entirety for all purposes. The latter are described in, for example, U.S. Pat. Nos. 5,258,668, 5,260,610, 5,260,611, and 5,436,575, and the 45 Altera Data Book, June 1996, all incorporated herein by reference in their entirety for all purposes.

Processing unit 101 may direct data to an appropriate system component for processing or storage, execute a program stored in memory 105 or input using I/O 111, or 50 other similar function. Processing unit 101 may be a central processing unit (CPU), microprocessor, floating point coprocessor, graphics coprocessor, hardware controller, microcontroller, programmable logic device programmed for use as a controller, or other processing unit. Memory 105 55 may be a random access memory (RAM), read only memory (ROM), fixed or flexible disk media, PC Card flash disk memory, tape, or any other storage retrieval means, or any combination of these storage retrieval means. PLD 121 may serve many different purposes within the system in FIG. I. 60 PLD 121 may be a logical building block of processing unit 101, supporting its internal and external operations. PLD 121 is programmed or configured to implement the logical functions necessary to carry on its particular role in system operation.

In a PLD, the number of available external pins limits the amount of data that may be input and output of the PLD at

the same time. The number of available external pins depends in part on the size and configuration of the package selected. Although larger package sizes provide greater numbers of external pins, it may not be desirable to use a larger package size since it will be more expensive, use more board space, and may have increased parasitics. Therefore, it is important to maximally use the available external pins for a given package.

On a typical PLD, some pins are dedicated for a particular purpose and other pins (i.e., I/O pins) are for input and output of logical data. For example, dedicated pins may be for testing or configuring the PLD. I/O pins are used to input and output user data. Dedicated pins cannot generally be used for user I/O. Therefore, the number of dedicated pins reduces the pins available for user I/O. Saving even a single dedicated pin, and using this pin instead for user I/O, may provide a great cost savings. For example, saving a single dedicated pin may avoid the use of the next larger package size.

In a PLD, there are typically dedicated pins for configuration and for testing. Configuration signals (e.g., pattern information) are input via a first set of dedicated pins. Test instructions and data (e.g., JTAG information) are input via a second set of dedicated pins. A technique to reduce the number of dedicated pins is to share the dedicated pins used for configuration and testing. The same amount of functionality would then be obtained using fewer dedicated pins This would increase the available number pins for user I/O. Although described with respect to PLDs, the techniques of the present invention are also applicable to other types of integrated circuits such as ASICs, microprocessors, and memories where it is desirable to reduce the number of dedicated pins and instead use these pins for user I/O.

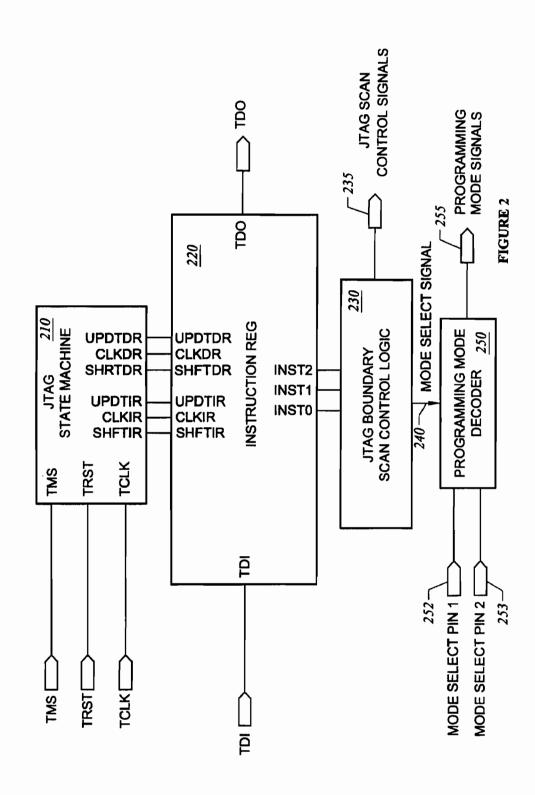

FIG. 2 shows a specific embodiment of the present invention. FIG. 2 shows a block diagram of JTAG circuitry and programming mode selection circuitry. JTAG circuitry is discussed in some detail in Altera's Application Note 39, "IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices," November 1995, incorporated herein by reference. In brief, the JTAG circuitry implements the IEEE 1149.1 specification or boundary-scan testing architecture. The JTAG circuitry can test pin connections without using physical test probes and can capture functional data while a device is operating normally.

The circuitry has JTAG dedicated pins TMS, TRST, TCLK, TDI, and TDO. Note that TRST pin may not be present in some embodiments. The TMS, TRST, and TCLK pins are coupled to a JTAG state machine 210. JTAG state machine 210 is a state machine providing output signals SHFTIR, CLKIR, UPDTIR, SHFTDR, CLKDR, and UPDTDR based on the TMS, TRST, TCLK inputs. JTAG state machine 210 controls the sequential operation of the circuitry.

TDI is a serial input to an instruction register 220, and TDO is a serial output. JTAG state machine 210 controls the serially shifting of an instruction from TDI into instruction register 220. The instruction may be serially shifted out through TDO. Further, the instruction may also be output in parallel via INST0, INST1, and INST2 lines. In the JTAG circuitry, there are also data registers (such as a boundary-scan register) that are not explicitly shown in FIG. 2. A description of the JTAG data registers may be found in Application Note 39.

The instruction is coupled to a JTAG boundary control scan control logic 230 via parallel INST0, INST1, and INST2 lines. JTAG boundary scan control logic 230 gener-

ates JTAG scan control signal 235. JTAG scan control signals 235 are routed to the appropriate JTAG circuitry to control JTAG operation. Further, JTAG boundary scan control logic 230 also generates a mode select signal 240 provided to a programming mode decoder 250. Programming mode decoder also has inputs from mode select pin 1 (252) and mode select pin 2 (253), and generates programming mode signals 255.

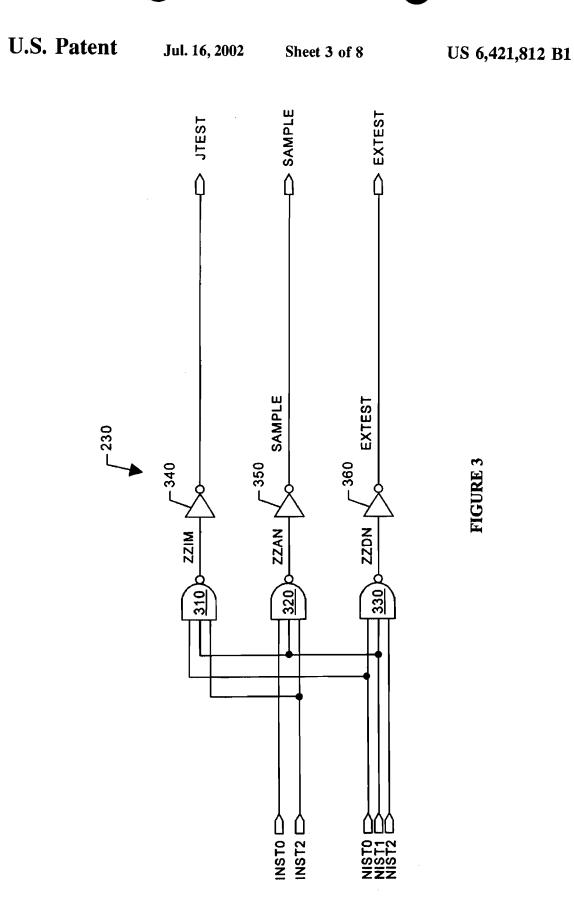

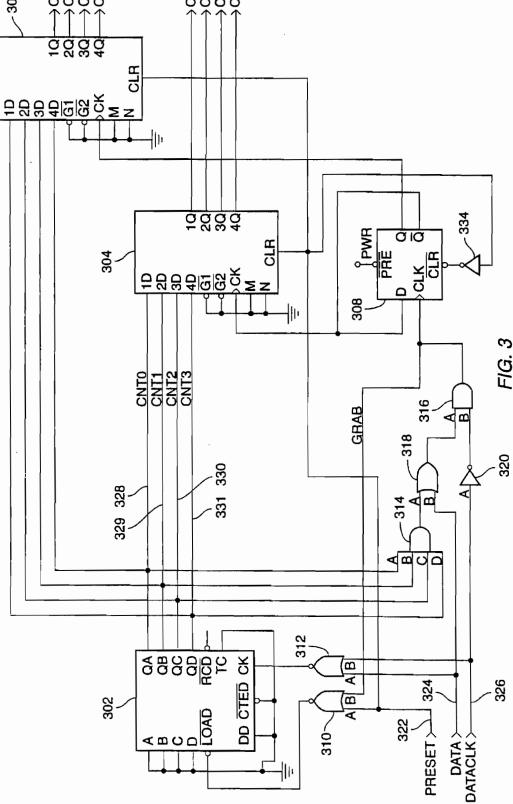

FIG. 3 shows a specific implementation of circuitry within JTAG boundary scan control logic 230. The input <sup>10</sup> signals are INST0, INST2, NINST0, NINST1, and NINST2. NINST0, NINST1, and NINST2 are the complements of INST0, INST1, and INST2, respectively. For example, NINST0, NINST1, and NINST2 may be obtained by inverting the INST0, INST1, and INST2 using inverters. Output <sup>15</sup> signals are JTEST, SAMPLE, and EXTEXT.

The circuitry includes NAND gates 310, 320, and 330. NAND gate 310 has as inputs NINST0, NINST1, and INST2. NAND 310 couples to an inverter 340 to output JTEST. NAND gate 320 has as inputs INST0, NINST1, and INST2. NAND 320 couples to an inverter 350 to output SAMPLE. NAND gate 330 has as inputs NINST0, NINST1, and NINST2. NAND 330 couples to an inverter 360 to output EXTEST.

The JTAG boundary scan control logic 230 circuitry determines which mode the PLD will be in based on the instruction input by the user. In this embodiment, the instruction has three bits, INST0, INST1, and INST2. In other embodiments, there may be more or less than three bits depending on the desired number of different instructions. For example, in some embodiments, the instruction has ten bits. With three bits, up to eight different instructions can be implemented. With ten bits, up to 2<sup>10</sup> different instructions can be implemented.

The circuitry in FIG. 3 decodes the instructions as follows. A "001" indicates a JTEST mode (where INST0 is 0, INST1 is 0, and INST2 is 1). A "101" indicates a SAMPLE mode. A "001" indicates an EXTEST mode. SAMPLE and EXTEST are JTAG modes. JTEST is a configuration or programming mode. Therefore, by using the same dedicated pins are used to input JTAG instructions, a programming mode may also be indicated. This means a separate declicated pin to indicate a programming mode is not needed, thus saving a dedicate pin which may be used instead for user I/O. Furthermore, there may be other JTAG modes (not shown in FIG. 3) such as BYPASS which is typically indicated by a "111" instruction.

In the SAMPLE and EXTEXT modes, the corresponding SAMPLE and EXTEST signals will be logic high. And, in the JTEST mode, the JTEST signal will be a logic high. SAMPLE and EXTEXT are examples of JTAG control signals 235. JTEST is an example of mode select signal 240.

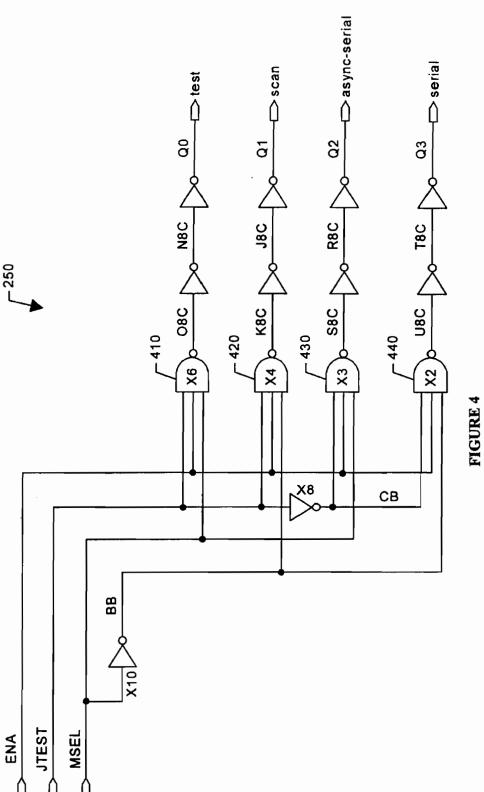

FIG. 4 shows circuitry for programming mode decoder 250. Inputs are ENA, JTEST, and MSEL. ENA is an enable signal to enable decoder 250. JTEST is generated by JTAG boundary scan control logic 230 (such as the circuitry shown in FIG. 3). MSEL is representative of mode select a pins 252 and 253. However, the implementation FIG. 4 only shows one mode select pin in order to illustrate the principles of the 60 present invention. In practice, there may be as many or as few mode select pins as desired to obtain the number of desired modes.

Outputs of decoder 250 are TEST, SCAN, ASYNC-SERIAL, and SERIAL. These signals are routed to the 65 appropriate programming circuitry to configure the PLD. The programming circuitry may generate high voltages such

as those used in the programming of Flash, EEPROM, EPROM, and other nonvolatile memory cells. The programming circuitry may also be used to configure other types of memory cells such as SRAM and DRAM cells.

The circuitry includes NAND gates 410, 420, 430, and 440. NAND gate 410 has inputs JTEST, ENA, and MSEL. NAND gate 410 outputs through a pair of serially coupled inverters to generate TEST. NAND gate 420 has inputs JTEST, ENA, and BB (i.e., complement of MSEL). NAND gate 420 outputs through a pair of serially coupled inverters to generate SCAN. NAND gate 430 has inputs CB (i.e., complement of JTEST), ENA, and MSEL. NAND gate 430 outputs through a pair of serially coupled inverters to generate ASYNC-SERIAL. NAND gate 440 has inputs CB, ENA, and BB. NAND gate 440 outputs through a pair of serially coupled inverters to generate SERIAL.

In operation, a "test" programming mode is entered when ENA is high, JTEST is high, and MSEL is high. A "scan" programming mode is entered when ENA is high, JTEST is high, and MSEL is low. An "async-serial" programming mode is entered when ENA is high, JTEST is low, and MSEL is high. A "serial" mode is entered when ENA is high, JTEST is low, and MSEL is low, and MSEL is low.

In practice, there are many implementations of the boundary scan control logic circuitry 230 and programming mode decoder 250 shown in FIGS. 3 and 4. Other implementations may use other selections for the decoding and other logical structures including AND and OR gates or look-up tables, to name a few examples.

For example, other specific instructions may be used to indicate a programming mode. Standard JTAG instructions are identified by 101, 000, and 111. Consequently, a programming mode control signal may be implemented by using an instruction or already used by JTAG. The available instructions are 001, 010, 011, 100, and 110. In FIG. 3, the choice of the specific instruction to indicate the JTEST programming mode was 001. However, any of the other available instructions could have been selected, and the appropriate changes made to the circuitry.

Furthermore, FIG. 3 only shows a single JTEST programming mode; however, circuitry may provide for more than one programming mode signal. With a 3-bit instruction, there can be up to five programming mode instructions. The circuitry can be modified to provide more than one programming mode instruction, and thus save greater numbers of dedicated mode select pins.

The circuitry shown in FIGS. 3 and 4 illustrates (by way of an specific example) a technique to eliminate one mode select pin by implementing a JTEST instruction. The JTEST instruction is recognized by the JTAG circuitry to indicate a programming mode. Using the JTEST signal, programming mode decoder 250 provides four modes, taking as input only one dedicated mode select pin. Without the JTEST instruction, two dedicated mode select pins would have been required to have four different programming modes. The JTEST instruction saves one mode select pin. Therefore, using the technique of the present invention, fewer dedicated pins are required to implement the programming modes, leaving more external pins for user I/O.

In further embodiments of the present invention, dedicated pins to indicate the programming modes may be eliminated altogether. In that case, the programming modes would be determined entirely by the instruction in instruction register 220. And there may be multiple JTEST signals. For example, an instruction may be decoded to provide JTEST1, JTEST2, and JTEST3 signals used to distinguish

between up to eight programming modes. As discussed above, the number of available programming modes depends on the number of available instructions not being used to implement JTAG modes.

The techniques and circuitry of the present invention are 5 also applicable for in-system programming (ISP) of a PLD, where the PLD is programmed while resident on a printed

FIG. 5 shows a flow diagram of a technique of the present invention. The technique of the present invention permits the 10 programming or configuration of an integrated circuit using the JTAG circuitry. In a step 501, an instruction is input into JTAG instruction register 220 of the integrated circuit. The instruction may be serially shifted in via the TDI pin according to the control signals from JTAG state machine 210. In a specific embodiment, the instruction may have three bits INST0, INST1, and INST2.

In a step 505, the instruction in the instruction register is decoded. The instruction is passed in parallel to JTAG boundary scan control logic 220. JTAG boundary scan 20 control logic 220 generates the appropriate control signal to indicate a JTAG mode or a programming mode. For example, SAMPLE and EXTEST are JTAG modes, and JTEST is a programming mode.

In a step 510, the JTEST signal is generated by JTAG 25 boundary scan control logic 220 to indicate a programming mode. The JTEST signal may be implemented using an available instruction which is not used as a JTAG instruc-

In a step 515, the JTEST signal is passed to programming mode decoder 250. In a step 520, using the JTEST signal, the programming mode decoder 250 generates programming mode signals 255 (such as TEST, SCAN, ASYNC-SERIAL, and SERIAL) that are passed to the programming circuitry.

Based on programming mode signals 255, the integrated circuit will be configured by the programming circuitry. The configuration of the integrated circuit may be in an in-system programming (ISP) mode.

The present invention may be used in conjunction and is 40 compatible with other techniques to effectively increase the available number of user I/O pins, such as described in U.S. patent application Ser. No. 09/094,226, filed Jun. 9, 1998, now U.S. Pat. No. 6,314,550, which is incorporated by reference.

Another technique to increase the number of pins is to permit the use of the JTAG pins for user I/O when JTAG is not used by the user. To implement the JTAG standard in an integrated circuit, the integrated circuit needs at least four pins: TCLK, TMS, TDIN, and TDO. These are dedicated 50 pins for accessing JTAG functionality. However, for customers who do not use JTAG, these pins are not used. The technique of the present invention allows these customers to use the JTAG pins as regular I/O pins. The technique of the present invention is especially useful for programmable 55 JTAG functionality is permitted. logic devices (PLDs), field programmable gate arrays (FPGAs), and many other types of integrated circuits.

In the method of the present invention, the information whether JTAG operation is enabled or disabled is encoded in an option register bit. After power up of the integrated 60 circuit, the default state of option register allows these four pins to be used as JTAG pins. Thus, JTAG operation is enabled. After the option register bit is programmed, there are two cases.

(1) The customer may choose to use JTAG, and the option 65 register is configured to reflect this. Then, these four pins will continue to function as JTAG pins.

(2) In the case the customer chooses not to use JTAG, the option register is configured to reflect this. The four JTAG pins will be disconnected from the JTAG circuitry. JTAG operation will not be enabled. After the device enters the user mode, these four pins can be used as regular I/O pins, thus avoiding the waste of these pins when JTAG is not used.

The configuration of the option register may be held using memory cells such as SRAM, EPROM, EEPROM, Flash, RAM, and many others. The configuration information may be nonvolatile.

During programming, the JTAG state machine stays in the reset state regardless the state of JTAG pins.

An advantage of the method of the present invention is to allow four more I/O pins for those customers who do not use JTAG. These customers can treat the four pins as regular I/O pins during both programming and user mode. Further, there is no "difficult to use" problem.

FIGS. 6, 7, and 8 show a circuit implementation for an integrated circuit with configurably or selectably enabled and disabled JTAG pins.

FIG. 6 shows circuitry which may be used for the TDl. TCLK, and TMS input pins. Pin 610 is the I/O pin of the integrated circuit, and is coupled to an output buffer 615. Output buffer 615 has transistor drivers coupled to a noisy positive supply VCCN and noisy ground supply VSSN. VCCN and VSSN are distinguished from quiet positive and ground supplies VCCQ and VSSQ, respectively. Some degree of isolation is achieved by separating the quiet and noisy supplies. However, in some implementations, there may be only VCC and VSS supply pins, where there are not separate noisy and quiet supplies.

Output buffer 615 is a data output buffer for drive data to pin 610. Output data is input at a DIN input. An OEB input controls whether pin 610 is tristated. A RNSLEW input controls whether the slew rate at the drivers of the output buffer are slowed in order to minimize or prevent ground or power bounce. A DATX output passes data from pin 610 to an input buffer for the integrated circuit. The input buffer includes inverters INV7 and INV6. An output of INV6 drives the internal circuitry.

An RJTAG input to the circuitry determines whether JTAG functionality is enabled or disabled. A JTAG input buffer is represented by block, the details of which are shown in FIG. 7. The JTAG input buffer includes inverters 710 and 720 and a transmission gate 725. An input of inverter 710 is coupled to DATX (see FIG. 6). A control electrode of an NMOS transistor of transmission gate 725 is coupled to RJTAG. A control electrode of a PMOS transistor of transmission gate 725 is coupled through an inverter 725 to RJTAG. An output of inverter 726 is also coupled to a gate of an NMOS transistor 740, which is coupled between an output 628 of the JTAG input buffer and ground.

When RJTAG is a logic high, the JTAG input buffer 620 is enabled to pass data to the internal JTAG circuitry and

When RJTAG is a logic low, JTAG functionality if disabled. This is occurs by disabling the JTAG input buffer. Transmission gate 725 is turned off, decoupling an output of inverter 720 from output 628 of the JTAG input buffer. Transistor 740 is turned on in order to ground output 628. A PMOS transistor 635 is turned on in order to couple VCC to the input of the JTAG input buffer 620, ensuring the input is a logic high. Then, inverters 720 and 710 will be in a known state, and not consume unnecessary power. RJTAG will control the output buffer 615 to function as a user I/O pin.

FIG. 8 shows circuitry which may be used for a TDO output pin. Depending on the states of RJTAG and JOEB, the JTAG functionality may be disabled. The input buffer (i.e., INV6 and INV7) and output buffer 615 are as described above. A circuit block is a JTAG output buffer 810 for outputting JTAG data. This JTAG data is input to the JTAG output buffer through the JDIN pin. An output of the JTAG 5 output buffer 810 is coupled to pin 610.

When RJTAG is logic high and JOEB is logic low, JTAG functionality will be enabled. When RJTAG is logic low and JOEB is logic high, JTAG functionality will be disabled. Specifically, the JTAG output buffer will be tristated, and output buffer 615 will function similarly as for a user I/O pin.

The foregoing description of preferred embodiments of the invention has been presented for the purposes of illustration and description. It is not intended to be exhaustive or to limit the invention to the precise form described, and many modifications and variations are possible in light of the teaching above. The embodiments were chosen and described in order to best explain the principles of the invention and its practical applications to thereby enable the others skilled in the art to best utilize and practice the invention in various embodiments and with various modifications as are suited to the particular use contemplated. It is intended that the scope of the invention be defined by the following claims.

What is claimed is:

1. A method of configuring a programmable integrated circuit comprising:

providing an instruction to a JTAG instruction register; passing the instruction to a JTAG boundary scan control logic block wherein the JTAG boundary scan control logic generates JTAG scan control signals;

generating in the JTAG boundary scan control logic block a control signal;

passing the control signal to a programming mode decoder; and

based on the control signal, generating a programming mode signal to place the programmable integrated circuit in a configuration mode.

- 2. The method of claim 1 wherein the instruction is not an IEEE 1149.1 JTAG instruction.

- 3. The method of claim 1 wherein the instruction is shifted serially into the JTAG instruction register.

4. The method of claim 1 wherein the instruction is passed 45

- 4. The method of claim 1 wherein the instruction is passed in parallel to the JTAG boundary scan control logic block.

- 5. The method of claim 1 wherein the control signal is not a JTAG scan control signal.

- 6. The method of claim 1 further comprising:

- in the configuration mode, loading configuration information into the programmable integrated circuit through non-JTAG external pins.

- 7. The method of claim 1 further comprising:

- configuring programmable memory cells of the programmable integrated circuit in the configuration mode.

- 8. The method of claim 7 wherein the programmable memory cells are EEPROM or Flash cells.

- 9. The method of claim 7 wherein the programmable memory cells are SRAM cells.

- 10. The method of claim 1 wherein the programming 60 mode decoder comprises:

- a plurality of logic gates, each having an input coupled to the control signal and at least two inputs coupled to mode select signals, and providing four separate programming mode signals.

- 11. A method of configuring a programmable integrated circuit comprising:

- storing in a JTAG instruction register an instruction indicating the programmable integrated circuit is to be configured;

- placing the programmable integrated circuit in a configuration mode based on the instruction stored in the JTAG instruction register; and

- configuring programmable memory cells of the programmable integrated circuit in the configuration mode.

- 12. The method of claim 11 further comprising:

- decoding the instruction using a JTAG boundary scan control logic block; and

- determining the instruction is not a JTAG scan control signal.

- 13. The method of claim 11 wherein configuring the programmable integrated circuit comprises imprinting the programmable integrated circuit with a desired pattern.

- 14. The method of claim 11 further comprising:

- in the configuration mode, selecting a configuration mode operation based on the instruction stored in the JTAG instruction register and a mode select pin.

- 15. The method of claim 11 wherein the programmable memory cells are EEPROM or Flash cells.

- 16. The method of claim 11 wherein the programmable memory cells are SRAM cells.

- 17. A method of operating a programmable logic device comprising:

- serially inputting an instruction to an instruction register of the programmable logic device;

- decoding the instruction in a control logic block;

- when the instruction is an IEEE 1149.1 JTAG instruction, performing IEEE 1149.1 JTAG operations in the programmable logic device;

- when the instruction is a configuration instruction, generating a control signal in the control logic block;

- in response to the control signal, generating a programming mode signal to place the programmable logic device into a configuration mode.

- 18. The method of claim 17 further comprising:

- when in the configuration mode, permitting a user to configure the programmable logic device.

- 19. The method of claim 17 wherein the configuration instruction is not a IEEE 1149.1 standard JTAG instruction.20. The method of claim 17 further comprising:

- when the instruction is not the configuration instruction, not placing the programmable logic device in the configuration mode.

- 21. The method of claim 17 further comprising:

- when in the configuration mode, permitting a user to select from a plurality of different modes within the configuration mode.

- 22. The method of claim 21 wherein the user's selection of one of the plurality of different modes is input by way of parallel instruction bits provided to the programmable logic device.

- 23. A technique of programming a programmable logic device while it is resident on a system board comprising the method recited in claim 17.

- 24. The method of claim 17 wherein the JTAG instruction comprises a plurality of bits clocked into the programmable logic device.

- 25. The method of claim 17 wherein the control logic block comprises a plurality of NAND gates, each coupled to the instruction register.

11

26. The method of claim 17 further comprising:

- mable integrated circuit in the configuration mode. 27. The method of claim 26 wherein the programmable memory cells are EEPROM or Flash cells.

configuring programmable memory cells of the program-

28. A method of placing a programmable logic integrated circuit into its configuration mode to program memory cells of the programmable logic integrated circuit comprising

inputting a configuration instruction into a register of the programmable logic integrated circuit, wherein the register is also used for IEEE 1149.1 JTAG operations when IEEE 1149.1 JTAG instructions are input into the register.

29. The method of claim 28 wherein the memory cells are EEPROM or Flash cells.

12

# United States Patent [19]

Cliff et al.

[11] Patent Number:

5,563,592

[45] Date of Patent:

Oct. 8, 1996

#### [54] PROGRAMMABLE LOGIC DEVICE HAVING A COMPRESSED CONFIGURATION FILE AND ASSOCIATED DECOMPRESSION

- [75] Inventors: Richard G. Cliff, Milpitas; L. Todd Cope, San Jose, both of Calif.

- [73] Assignee: Altera Corporation, San Josc, Calif.

- [21] Appl. No.: 156,561

- [22] Filed: Nov. 22, 1993

- [58] Field of Search ...... 341/63, 64; 364/715.03,

364/715.02, 715.09

#### [56]

#### References Cited

#### U.S. PATENT DOCUMENTS

| 4,446,516 5/1984  | Nishimura 341/63          |

|-------------------|---------------------------|

| 4,791,660 12/1988 | 379/88 Oye et al 379/88   |

| 5,258,932 11/1993 | 364/578 Matsuzaki 364/578 |

| 5,260,610 11/1993 | Pedersen et al 326/41     |

| 5,260,611 11/1993 | 326/39 Cliff et al 326/39 |

| 5,440,718 8/1995  | 6 Kumagai et al 395/481   |

|                   |                           |

#### FOREIGN PATENT DOCUMENTS

0500267 8/1992 European Pat. Off. .

### OTHER PUBLICATIONS

Jock Tomlinson et al., "Designing with reprogrammable FPGAs", Australian Electronics Engineering, Feb. 1993, 67-70.

Shih-Fu Chang et al., "Designing High-Throughput VLC Decoder Part 1—Concurrent VLSI Architectures", *IEEE Transactions on Circuits and Systems for Video Technology*, (Jun. 1992) 2:2:187-96.

Ming-Ting Sun et al., "High-Speed Programmable ICs for Decoding of Variable-Length Codes", SPIE, (1989) 1153:28-39.

Shih-Fu Chang et al., "VLSI Designs for High-Speed Huffman Decoder", IEEE International Conference on Computer Design: VLSI in Computers and Processors, (1991), pp. 500-503.

J. C. Vermeulen, "Logarithmic Counter Array with Fast Access", *IBM Technical Disclosure Bulletin*, (Nov. 1984), 27:6:3380-3381.

Primary Examiner—Howard L. Williams

Attorney, Agent, or Firm—Townsend and Townsend and

Crew LLP

#### [57]

#### ABSTRACT

A method of utilizing compression in programming programmable logic devices is disclosed. The present invention compresses the configuration file to be used in programming a programmable logic device. The compression step reduces the size of the configuration file. The reduction in the size of the compression file results in the reduction in the size of the memory device used to store the configuration file before it is used to program the programmable logic device.

#### 34 Claims, 8 Drawing Sheets

Sheet 1 of 8

100

FIG. 1

Oct. 8, 1996

FIG. 2

Oct. 8, 1996

FIG. 6

FIG. 7

FIG. 8

FIG. 9

### PROGRAMMABLE LOGIC DEVICE HAVING A COMPRESSED CONFIGURATION FILE AND ASSOCIATED DECOMPRESSION

### BACKGROUND OF THE INVENTION

The present invention relates to the field of data processing. In particular, it relates to the use of data compression in for transmitting and storing configuration data for programming programmable logic devices.

Today's advanced technology has provided for design, development and manufacturing of complicated programmable logic devices. Such devices include those described in U.S. Pat. Nos. 5,260,610 and 5,260,611, incorporated herein by reference for all purposes. These devices include numer- 15 ous programmable elements to provide flexibility. By programming these programmable elements, the user defines the function that the programmable logic device must perform. Configuration files are used to program the programmable logic devices. A typical configuration file includes at least one memory pattern. The memory pattern includes a series of low "0" and high "1" bits which are used to program the individual programming elements. Configuration files are stored on the PLD or in memory associated with the PLD and are loaded onto the PLD at power-up or 25 ing to the present invention; when the PLD system receives a signal to reconfigure the

Typically, a configuration file includes more than one memory pattern. It is also possible that more than one configuration file are used to program a typical programmable logic device. The configuration files are usually stored in memory banks and are individually retrieved to program the corresponding programmable logic device. Typically, EPROMs are used to store the configuration files.

As the complexity of the programmable logic devices grows, so does the number of programmable elements used. This requires configuration files with a greater number of "1s" and "0s" to program the programmable memory devices. As the size of the configuration files increases, so does the size of the EPROMs needed to store them. Large EPROMs are expensive and require large silicon area to be manufactured. The size of the silicon area is more important when the EPROM is manufactured on the same substrate as the programmable logic device. The size of the EPROMs limit the complexity of the programmable logic device.

From the foregoing, it can be appreciated that there is a need for an apparatus and method of reducing the size of the configuration files before they are stored in memory, particularly where the configuration files are stored in memory 50 located on the same substrate as the PLD.

### SUMMARY OF THE INVENTION

The method and apparatus of the present invention compress the data file which is used to program a particular programmable logic device. The compressed data file is then stored in a memory element. Once it is necessary to program the programmable logic device, the compressed data file is decompressed and then is used to program the program- 60 mable logic device.

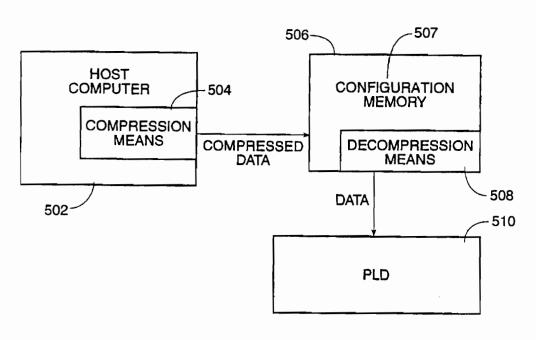

In one embodiment of the present invention, the compression and decompression are done by hardware. In a second embodiment, the compression is done by software external to the PL and the decompression is done by 65 hardware either located on the PLD, or closely associated with the PLD and an external configuration file memory.

Therefore, the present invention offers a solution to the problems caused by storage of large memory patterns that are used in programming the programmable logic devices.

Other advantages of the present invention will be more evident as the invention is disclosed in the ensuing detailed description of the invention and claims.

### BRIEF DESCRIPTION OF THE DRAWINGS

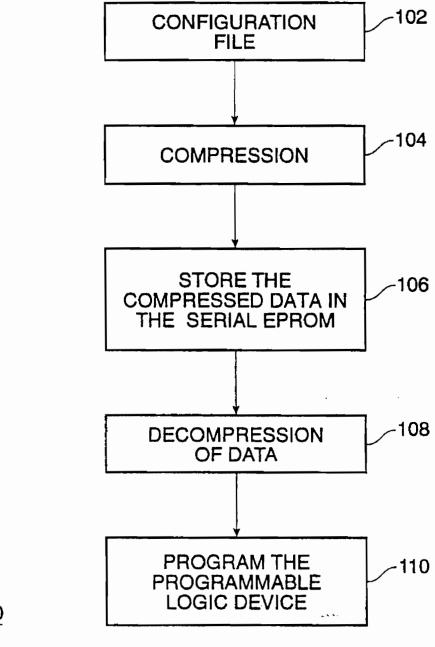

FIG. 1 illustrates the preferred embodiment of the method of the present invention;

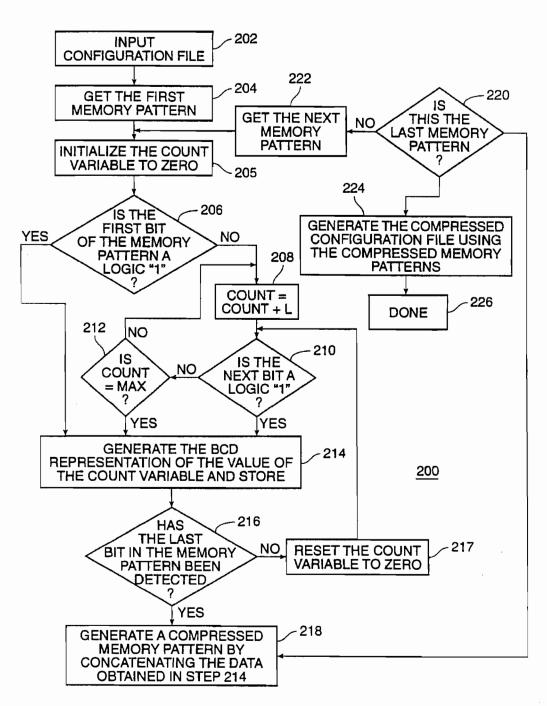

FIG. 2 is a flow chart showing the preferred method of performing the compression in the present invention;

FIG. 3 shows a circuit diagram of a compression circuit;

FIG. 4 shows the timing diagram of the circuit of FIG. 3 used to compress an example configuration file;

FIG. 5 is a flow chart which illustrates an alternative method in performing the compression in the present inven-

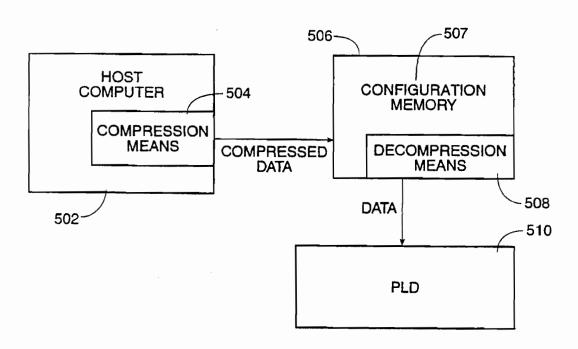

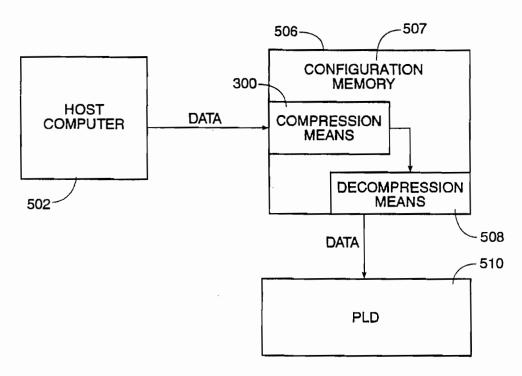

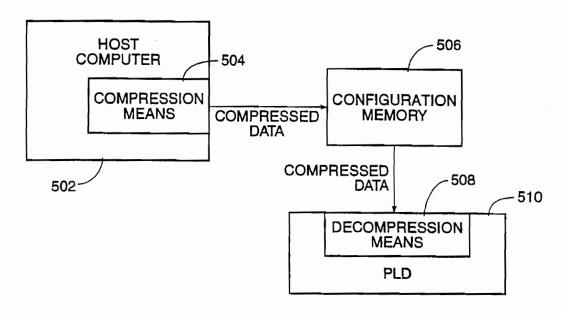

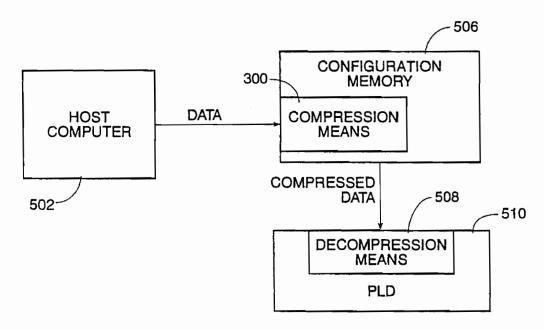

FIG. 6 shows one embodiment of the system according to the present invention;

FIG. 7 shows a second embodiment of the system accord-

FIG. 8 shows a third embodiment of the system according to the present invention;

FIG. 9 shows a fourth embodiment of the system according to the present invention; and

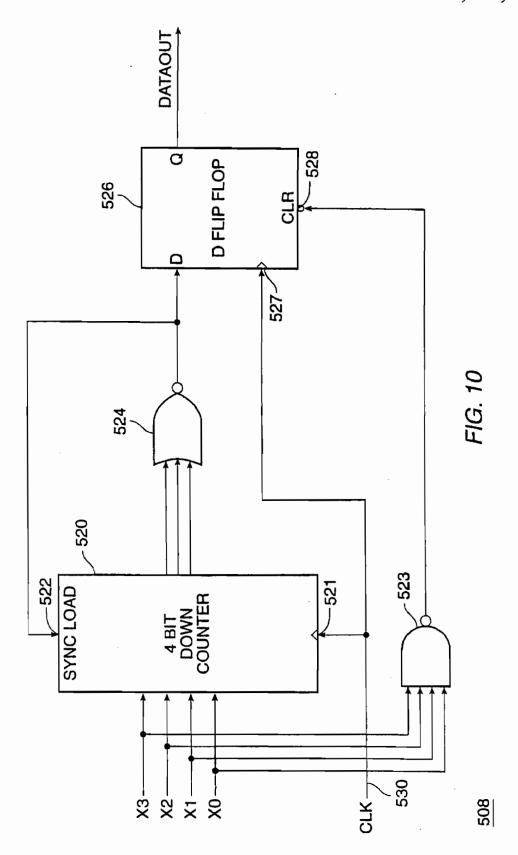

FIG. 10 shows a circuit diagram of a decompression circuit used in the present invention.

### DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

The present invention offers a solution to the problem of storing large configuration files. By reducing the number of bits in an individual configuration file through compression, the present invention eliminates the need for large memory elements either associated with or on the PLD in which to store them.

FIG. 1 illustrates a flow chart showing the steps of the method of the present invention. Process 100 first inputs the configuration file in step 102. The configuration file is then compressed in step 104 using a software compression algorithm or a hardware compression circuit. The compression step reduces the number of bits in the configuration file by a ratio of as much as 2 to 1. The compressed configuration file is then stored in a memory element, such as a serial EPROM, in step 106. Since the size of the generated configuration file is substantially smaller than the original configuration file, a memory element with smaller storage capacity can be used to store the generated file.

To program the programmable logic device, the original configuration file must be recreated. In step 108, the compressed configuration file is decompressed using a decompression circuit. Finally, in step 110, the configuration file generated in step 108 is used to program the programmable logic device.

In addition to reducing the size of the memory element, the reduction of the size of the individual configuration files allows for storing more than one configuration file in a single memory element. This eliminates the need for multiple memory elements where more than one configuration file can be used to program a programmable logic device.

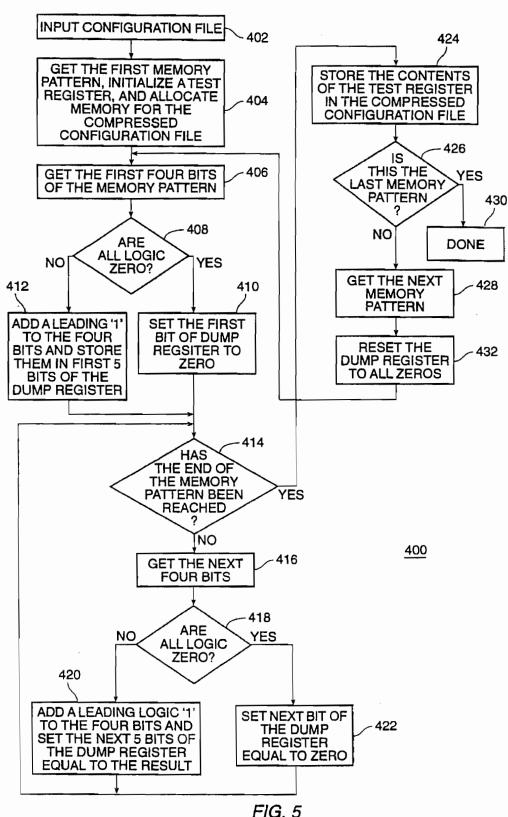

As mentioned above, the compression step can be performed by software or hardware. The flow chart of FIG. 2 shows the preferred method of performing the compression step 104 in FIG. 1. The compression process shown in FIG. 2 begins by inputting a configuration file as shown in step 5 202. This configuration file is typically stored in the memory of the host processing unit. This processing unit (shown in FIGS. 6 and 7) executes the software realizing the steps shown in the flowchart FIG. 2. As mentioned above, a typical configuration file includes at least one memory 10 pattern which is used to program the programmable logic device. However, almost always, configuration files include more than one memory pattern.

Process 200 continues by obtaining the first memory pattern to be compressed in step 204. In step 205, the value of a count variable is initialized to zero. The count variable is used to keep track of the number of low bits between two high bits in the memory pattern. As mentioned above, a low bit refers to a logic "0" bit and a high bit refers to a logic "1" bit. In step 206, the first bit of information in the memory pattern is examined. If the first bit is a high bit, the process proceeds to step 214, which will be described later.

If the first bit is a low bit, process 200 increments the value of the count variable and proceeds to step 210. In step 210, the next bit is examined. If the next bit is a high bit, process 200 proceeds to step 214. If the next bit is a low bit, process 200 proceeds to step 212. In step 212, the value of the count variable is examined to determine whether it has reached a maximum preset value. If the value of the count variable is equal to the maximum value, then process 200 proceeds to step 214, otherwise, it returns to step 208 and proceeds as explained above.

The maximum preset value of the count variable depends on the representation scheme used in step 214. For example, in the embodiment of the present invention, a Binary Coded Hexadecimal Representation ("BCH") representation of the value of the count variable is generated at step 214. It is well known in the art that four bits are used to generate the BCH representation of a single hexadecimal digit number. It is also well known that the maximum hexadecimal decimal number that can be represented by four bits is hexadecimal F or decimal fifteen. Therefore, in the present embodiment, the maximum preset value of the count variable is set to fifteen. Obviously, this number can change depending on the different schemes used to represent the value of the count variable.

Three different alternatives to reach step 214 are described above. While in step 214, process 200 generates the BCH representation of the value of the count variable. The outcome of step 214 is stored in memory and will be retrieved later to construct the compressed configuration file. In step 216, process 200 determines whether the last bit in the memory pattern was just examined. If the answer to step 216 is no, process 200 resets the value of the count variable to zero in step 212, returns to step 210, and proceeds as described above. If the answer to step 216 is yes, process 200 constructs the compressed memory pattern by retrieving and concatenating the BCH representations of the current memory pattern. The compressed memory pattern is stored in the memory of the host processor.

After step 218, process 200 proceeds by determining whether the current memory pattern is the last memory pattern in the configuration file in step 220. If the answer is no, process 200 retrieves the next memory pattern in the 65 configuration file from the memory of the host processor, returns to step 205, and continues as described above. If the

answer to step 220 is yes, process 200 generates the compressed version of the configuration file in step 224. This is done by retrieving the compressed memory patterns from the memory of the host processor and forming a file from all compressed memory patterns.

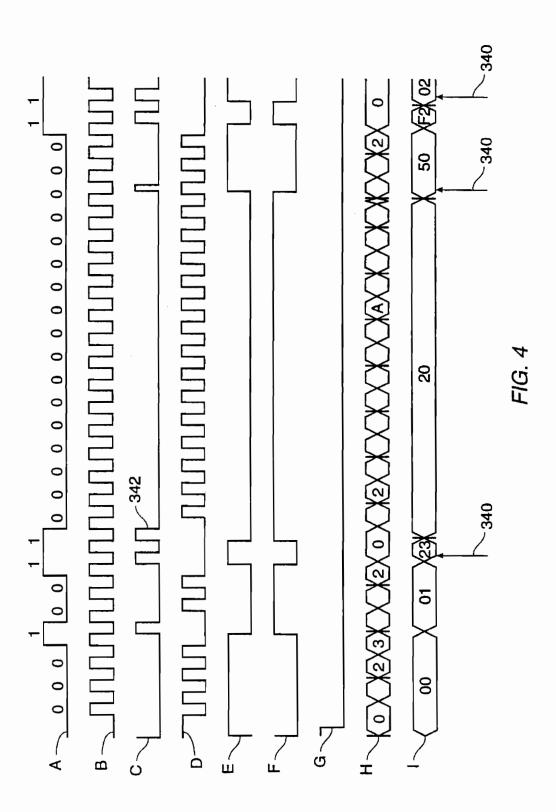

FIG. 3 illustrates an electronic circuit 300 which performs the compression step 104 in FIG. 1 using hardware. Circuit 300 includes a counter 302, 4-bit registers 304 and 306, "D" flip-flop ("FF") 308, NOR gates 310 and 312, 4-input AND gate 314, AND gate 316, OR gate 318, and invertors 320 and 334

Counter 302 is used to count the number of low bits between two high bits in a memory pattern. Counter 302 includes four inputs A-D, a LOAD input which is asserted when connected to a low level signal, a clock input "CK", and four outputs 328-332. It should be realized that a low level signal is realized by providing ground potential at the prospective inputs. The information on inputs A-D when loaded in counter 302 provides the initial count value of counter 302. In operation, counter 302 counts up or down from this initial count value. For example, if inputs A and B carry a low level signal and inputs C and D carry a high level signal, the initial value of counter 302 is three. In the embodiment of FIG. 3, inputs A-D are permanently connected to a low level signal. Outputs 328-331 carry the binary equivalent of the latest count value of the counter. Inputs A-D are loaded in counter 302 when a low level signal appears on LOAD input 332.

Outputs 328-331 are connected to inputs 1D-4D of both 4-bit registers 304 and 306. This allows for latching the information on outputs 328-331 in registers 304 and 306. Each of the two registers 304 and 306 further includes a clear input ("CLR"), a clock input and other inputs that are connected to ground potential as shown in FIG. 3. The CLR input of both registers 304 and 306 are connected to GRE-SET signal 322. GRESET input is used to initialize circuit 300, as will be described later. The CK input of register 304 is connected to the inverse Q output of FF 308 and the CK input of register 306 is connected to the Q output of FF 308.

The D input of FF 308 is connected to its inverse Q output and its clock input is connected to the output of AND gate 316. The signal at the output of AND gate 316 is also referred to as the GRAB signal 336. As it will be more clearly described below, a high to low or a low to high transition of the GRAB signal is used to latch the information on outputs 328-331. FF 308 further includes a CLR input which is connected to the output of invertor 334. Invertor 334 generates a clear signal to clear FF 308 by inverting the GRESET signal 322. The A input of AND gate 316 is connected to the output of OR gate 318, and the B input of AND gate 316 is connected to the output of invertor 320. The input of invertor 320 is connected to DATACLK signal 326, which is the system clock signal. The A input of OR gate 318 is connected to the output of AND gate 314 and its B input is connected to the DATA input terminal 324. The individual bits of each memory pattern serially enters compression circuit 300 via DATA input terminal 324.