|          |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 540          |  |

|----------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|

| ł        | CHRIS R. OTTENWELLER (STATE BAR NO. 73649)<br>cottenweller@orrick.com                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t-FILMIN     |  |

| 2        | G. HOPKINS GUY, III (STATE BAR NO. 124811)                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 3        | VIČKIE L. FEEMAN (STATE BAR NO. 1774                                                                      | CHRIS R. OTTENWELLER (STATE BAR NO. 73649)<br>cottenweller@orrick.com<br>G. HOPKINS GUY, III (STATE BAR NO. 124811)<br>hopguy@orrick.com<br>VICKIE L. FEEMAN (STATE BAR NO. 177487)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |  |

| 4        | vfeeman@orrick.com<br>BAS DE BLANK (STATE BAR NO. 191487)                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 5        | basdeblank@orrick.com<br>ORRICK, HERRINGTON & SUTCLIFFE LLP                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 6        | 1000 Marsh Road<br>Menlo Park, CA 94025                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 7        | Telephone: +1-650-614-7400<br>Facsimile: +1-650-614-7401                                                  | North C. S. W. 2011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |  |

| 8        | Attorneys for Plaintiff<br>APPLE INC.                                                                     | A Construction of the cons | 9            |  |

|          |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 10       | UNITED STATES DISTRICT COURT                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 11       | NORTHERN DISTR                                                                                            | ICT OF CALIFORNIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |  |

| 12       |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | HRL.         |  |

| 13       | APPLE INC., a California corporation,                                                                     | COMPLAINTFOR DECLARA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 ()         |  |

| 14       | Plaintiff,                                                                                                | COMPLAINT FOR DECLARA<br>JUDGMENT OF NON-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>T</b> ORY |  |

| 15       | ν.                                                                                                        | INFRINGEMENT AND INVA<br>OF PATENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LIDITY       |  |

| 16<br>17 | S3 GRAPHICS CO., LTD., a Cayman Islands<br>corporation, and S3 GRAPHICS, INC., a<br>Delaware corporation, | DEMAND FOR JURY TRIAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |  |

| 18       | Defendants.                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 19       |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 20       |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 21       |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 22       |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 23       |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 24       |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 25       |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 26       |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 27       |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

| 28       |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |

|          | OHS West:261056792.3                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | COMPLAINT    |  |

| 1  | Plaintiff Apple Inc. ("Apple") alleges against Defendants S3 Graphics Co., Ltd. ("S3G              |  |  |

|----|----------------------------------------------------------------------------------------------------|--|--|

| 2  | Cayman") and S3 Graphics, Inc. ("S3G Delaware") (collectively, "S3 Graphics") as follows:          |  |  |

| 3  | NATURE OF THE ACTION                                                                               |  |  |

| 4  | 1. This is an action brought pursuant to the Declaratory Judgment Act, 28 U.S.C.                   |  |  |

| 5  | § 2210, for a declaratory judgment of non-infringement and invalidity of patents S3 Graphics has   |  |  |

| 6  | asserted against Apple in proceedings before the United States International Trade Commission.     |  |  |

| 7  | 2. Apple seeks a declaratory judgment of non-infringement and invalidity of United                 |  |  |

| 8  | States Patent Nos. 6,658,146 ("the '146 Patent") (attached as Exhibit A); 6,683,978 (the "the '978 |  |  |

| 9  | Patent") (attached as Exhibit B); 6,775,417 ("the '417 Patent") (attached as Exhibit C); and       |  |  |

| 10 | 7,043,087 ("the '087 Patent") (attached as Exhibit D) (collectively, "the Asserted Patents") under |  |  |

| 11 | the Patent Laws of the United States, 35 U.S.C. §§ 101, et seq.                                    |  |  |

| 12 | THE PARTIES                                                                                        |  |  |

| 13 | 3. Plaintiff Apple is a California corporation with its principal place of business at             |  |  |

| 14 | 1 Infinite Loop, Cupertino, California 95014.                                                      |  |  |

| 15 | 4. On information and belief, Defendant S3G Cayman is a Cayman Islands                             |  |  |

| 16 | corporation with its principal place of business at 2nd Floor, Zephyr House, Mary Street, P.O.     |  |  |

| 17 | Box 709, Grand Cayman, Grand Cayman Islands, British West Indies.                                  |  |  |

| 18 | 5. On information and belief, Defendant S3G Delaware is a Delaware corporation                     |  |  |

| 19 | with its principal place of business at 1025 Mission Court, Fremont, California, 94539. On         |  |  |

| 20 | information and belief, S3G Delaware is a wholly owned subsidiary of S3G Cayman.                   |  |  |

| 21 | JURISDICTION AND VENUE                                                                             |  |  |

| 22 | 6. Apple brings this action under the Declaratory Judgment Act, 28 U.S.C. § 2201,                  |  |  |

| 23 | for a declaratory judgment of non-infringement and invalidity of the Asserted Patents under the    |  |  |

| 24 | Patent Laws of the United States, 35 U.S.C. §§ 101 et seq. This Court has subject matter           |  |  |

| 25 | jurisdiction pursuant to 28 U.S.C. §§ 1331 and 1338(a).                                            |  |  |

| 26 | 7. This Court has personal jurisdiction over S3G Cayman because S3G Cayman has                     |  |  |

| 27 | constitutionally sufficient contacts with California to make personal jurisdiction proper in this  |  |  |

| 28 | Court. On information and belief, S3G Cayman does business in the Northern District of             |  |  |

|    | OHS West:261056792.3 - 1 - COMPLAINT                                                               |  |  |

|    |                                                                                                    |  |  |

California, including business conducted through its subsidiary S3G Delaware.

8. On information and belief, S3G Cayman has negotiated and entered into to

licenses under the Asserted Patents with other entities in the Northern District of California,

including S3G Delaware. On information and belief, S3G Cayman derives the benefit of these

licenses, including benefits arising out of activities in California.

9. Further, on information and belief, S3G Delaware acts as the general agent of S3G

Cayman in that it was established for, and is engaged in, activities that, but for the existence of

the subsidiary, the parent would have to undertake itself. For example, on information and belief,

S3G Delaware engages in licensing activities out of its Fremont, California facility on behalf of

S3G Cayman relating to patents owned or controlled by S3G Cayman, including the Asserted

Patents.

12 10. On information and belief, S3G Delaware is an alter ego of S3G Cayman in that 13 the subsidiary is the mere instrumentality of the parent and there is such unity of interest and 14 ownership that the separate personalities of the two entities no longer exist. On information and 15 belief, S3G Cayman controls the activities of S3G Delaware, and the two entities do not maintain 16 separate, distinct businesses.

17

28

1

11. Venue in this district is established under 28 U.S.C. §§ 1391(b) and (c).

An actual controversy exists between S3 Graphics and Apple as to whether Apple 18 12. infringes the Asserted Patents. On May 28, 2010, S3 Graphics filed a complaint (the "ITC 19 Complaint") with the United States International Trade Commission under section 337 of the 20Tariff Act of 1930. The ITC Complaint alleges that Apple infringes the Asserted Patents through 21 the manufacture and distribution of certain hardware and software products. The ITC Complaint 22 further alleges that Apple contributes to and induces infringement of the Asserted Patents by 23 others. A true and correct copy of the ITC Complaint is attached hereto as Exhibit E. 24 25 BACKGROUND

26 13. On information and belief, the Asserted Patents were issued by the United States

27 Patent and Trademark Office and are assigned to S3G Cayman.

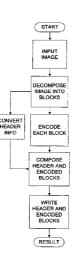

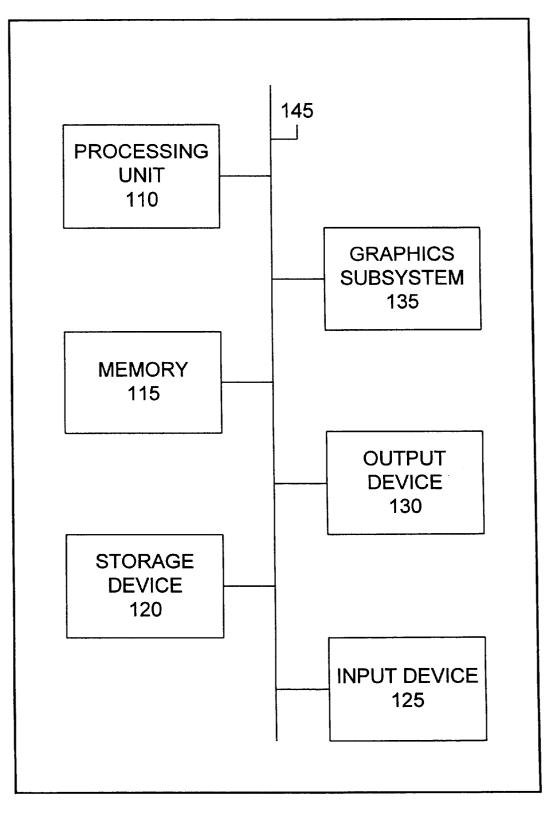

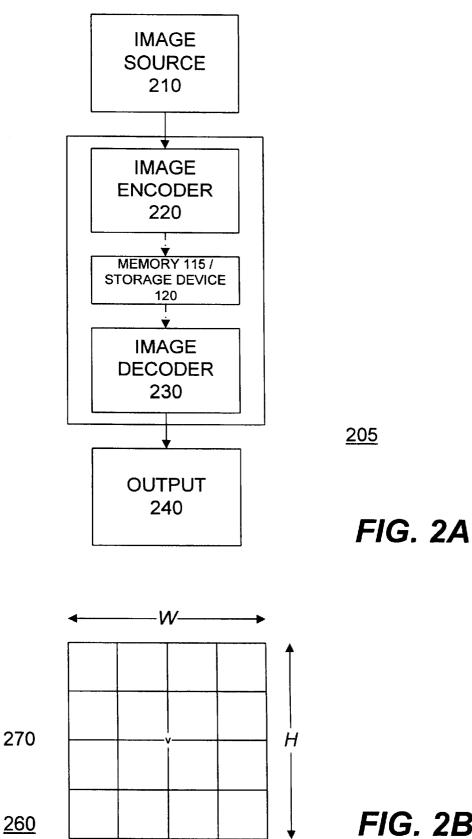

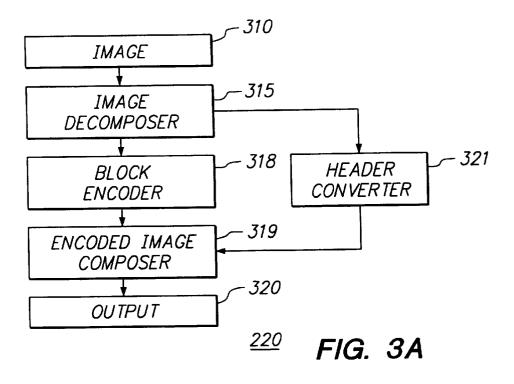

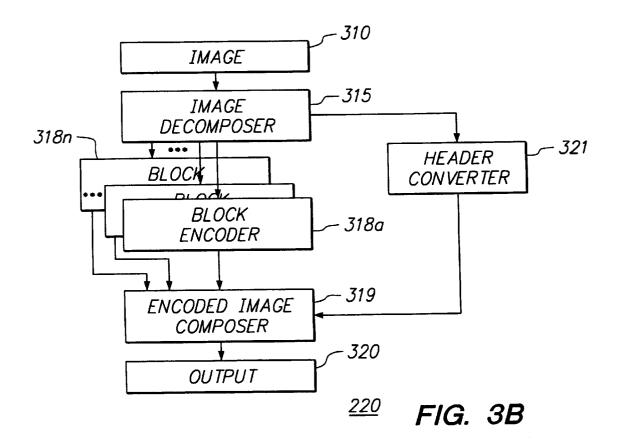

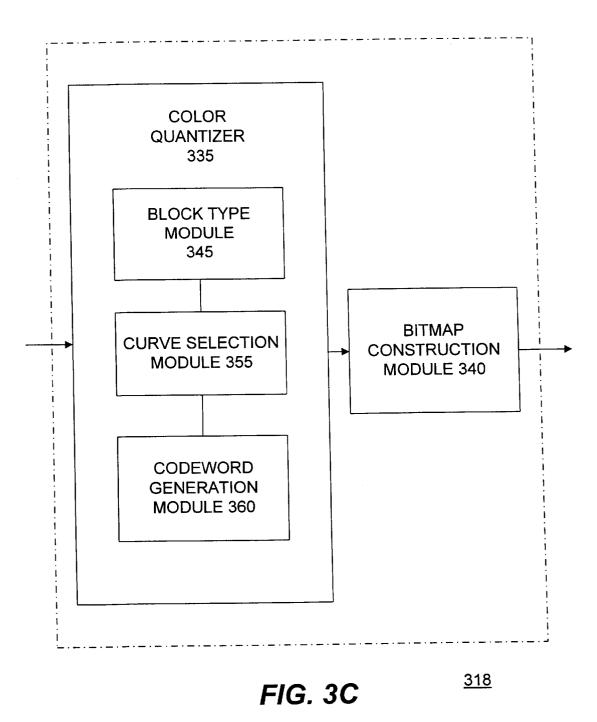

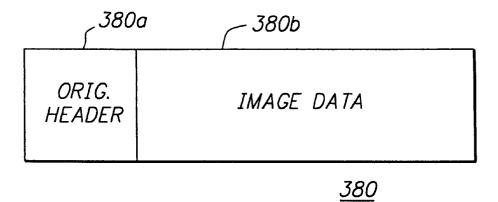

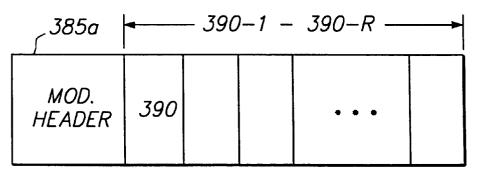

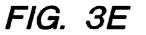

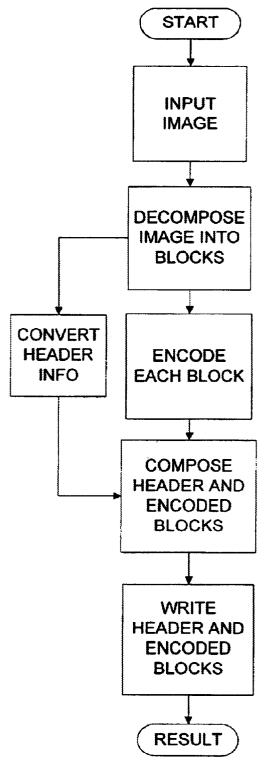

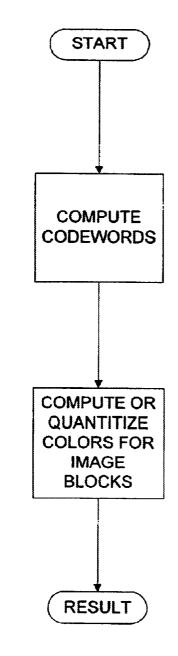

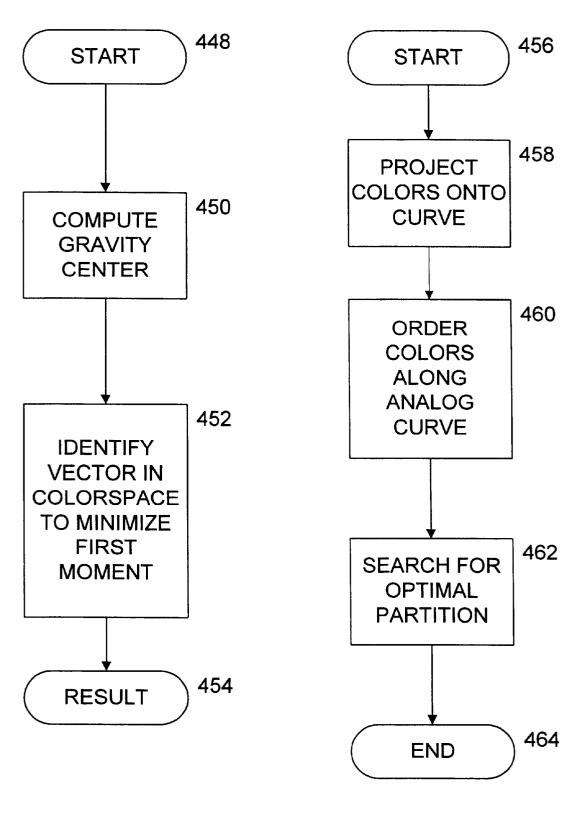

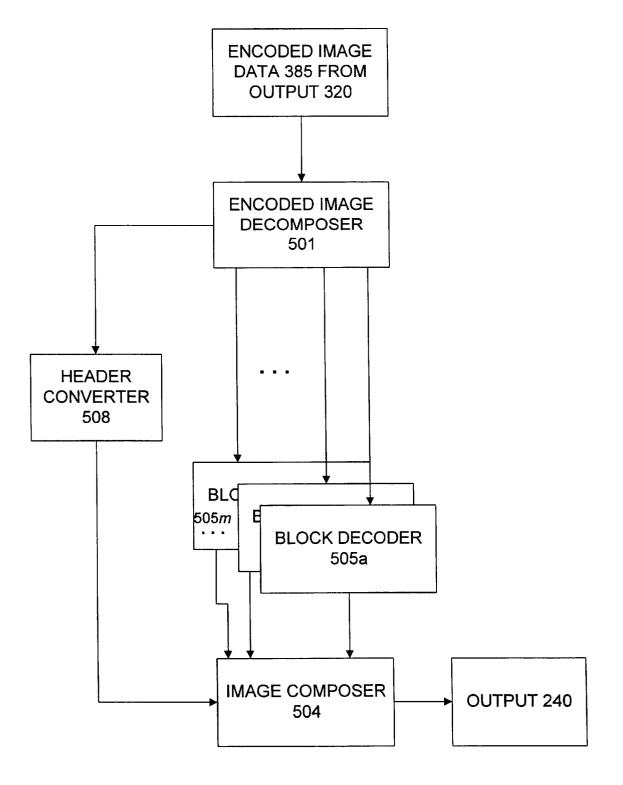

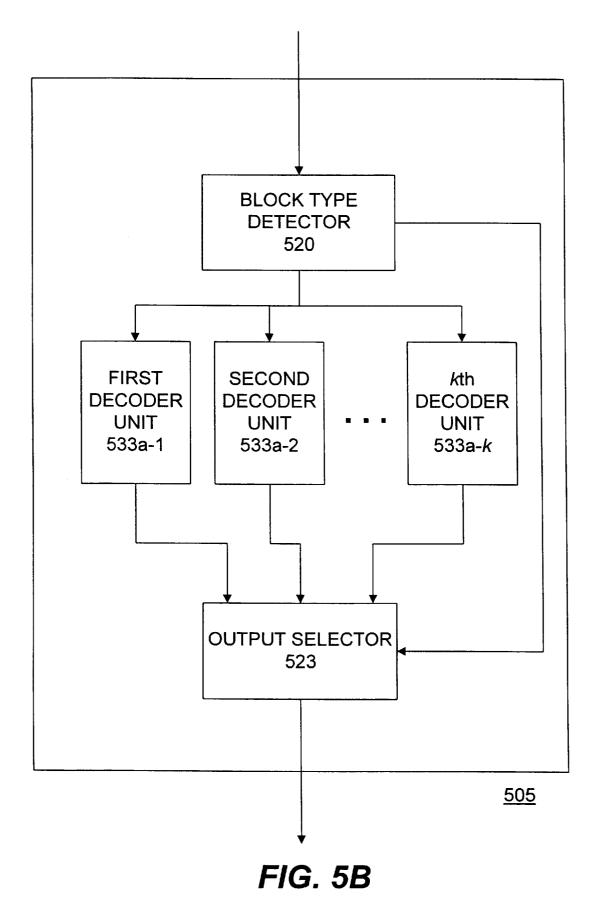

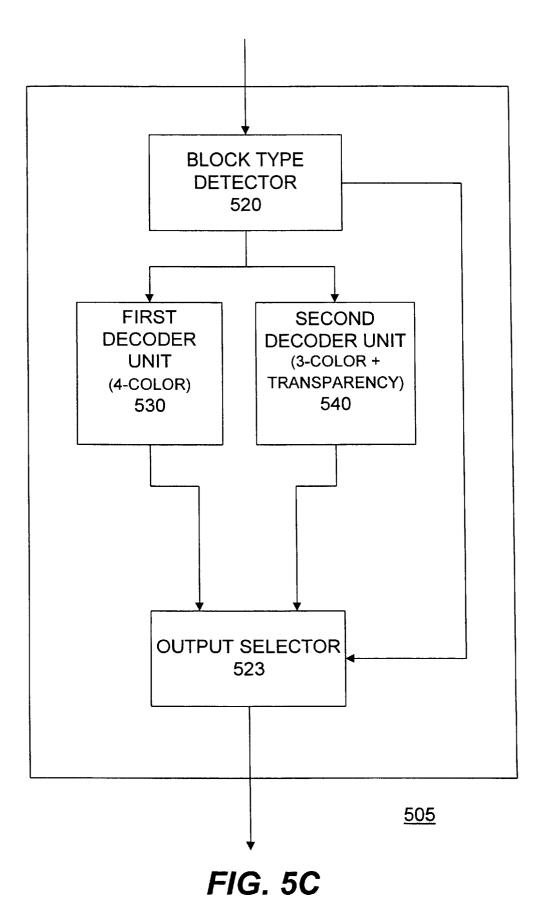

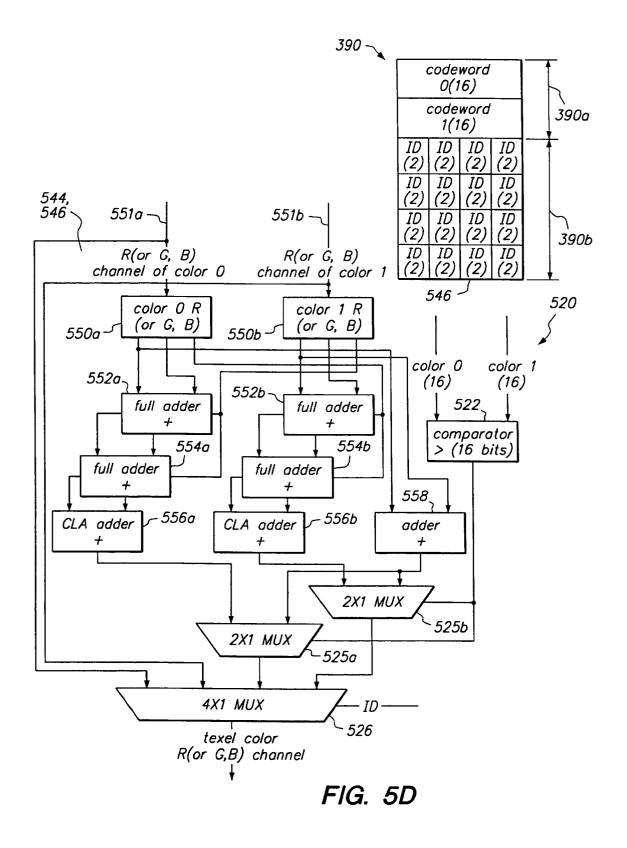

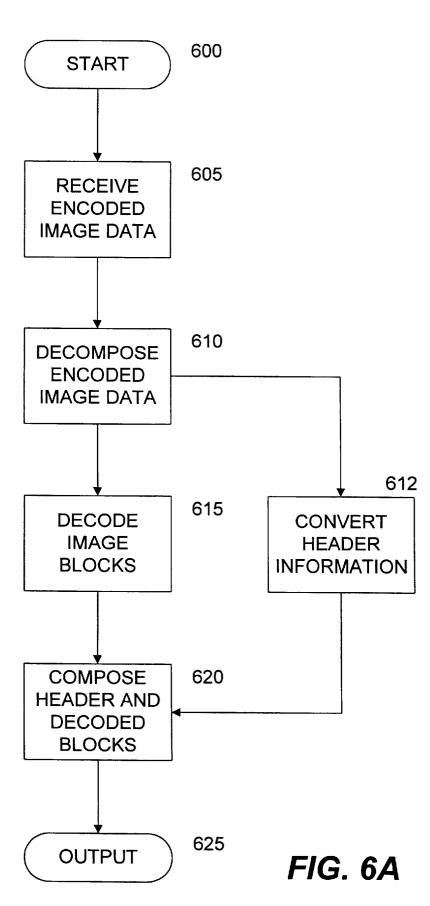

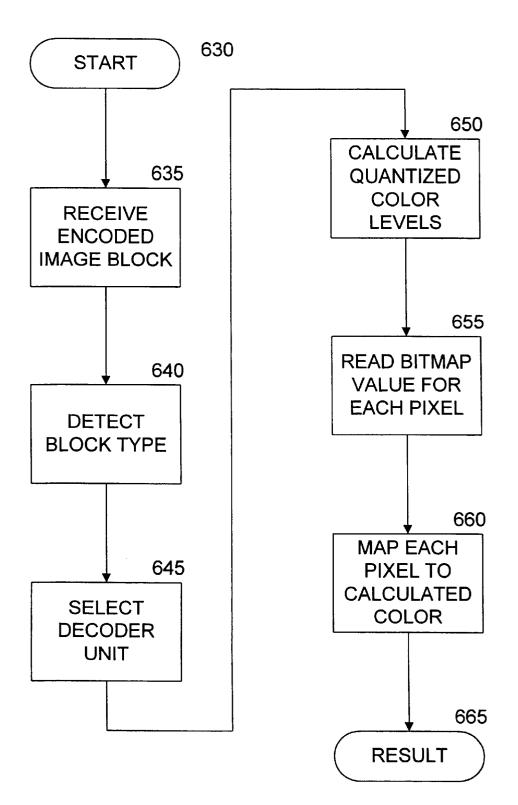

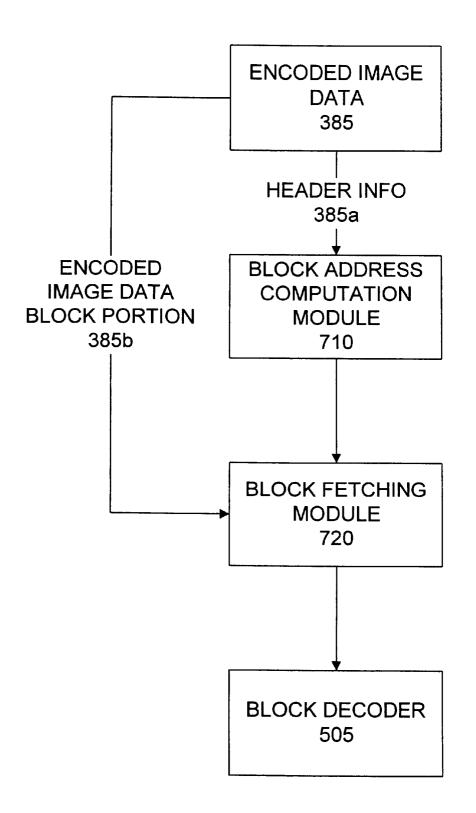

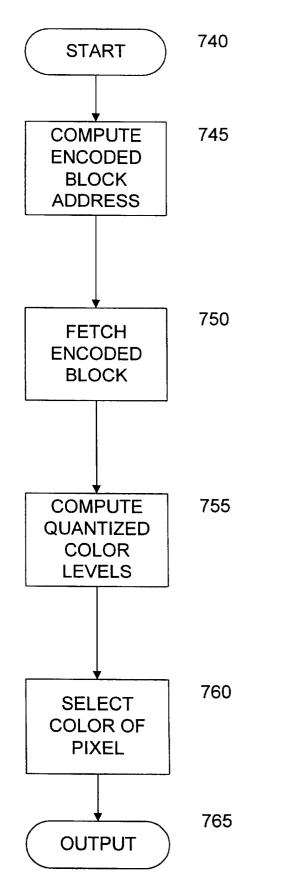

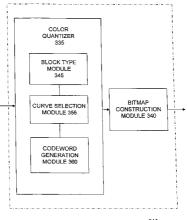

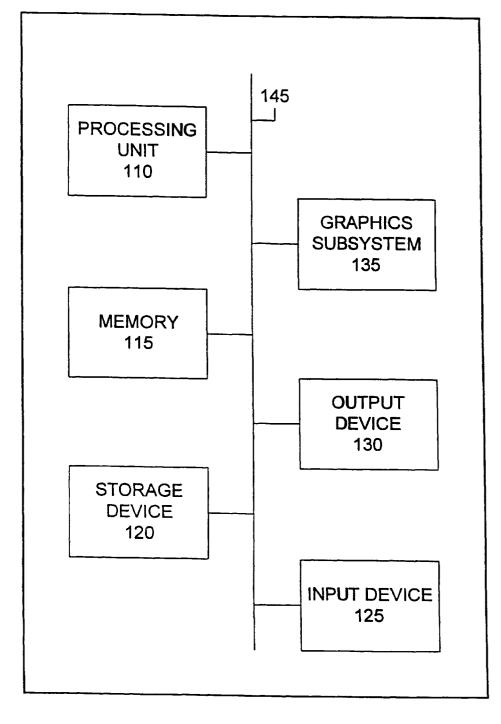

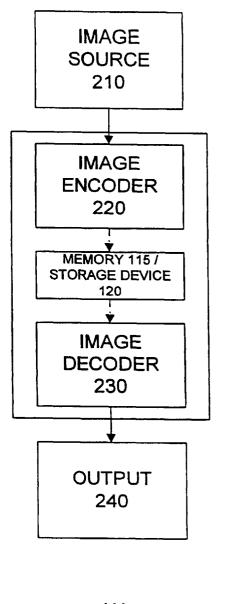

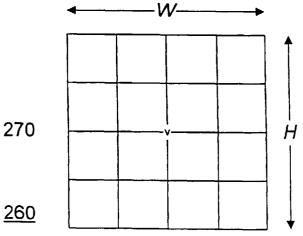

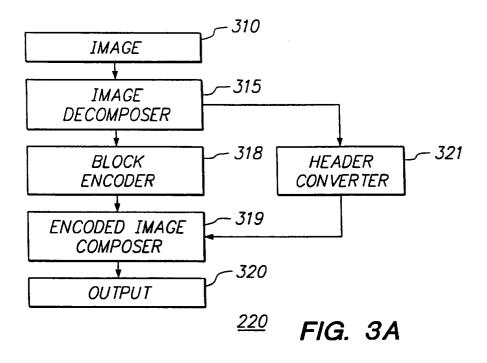

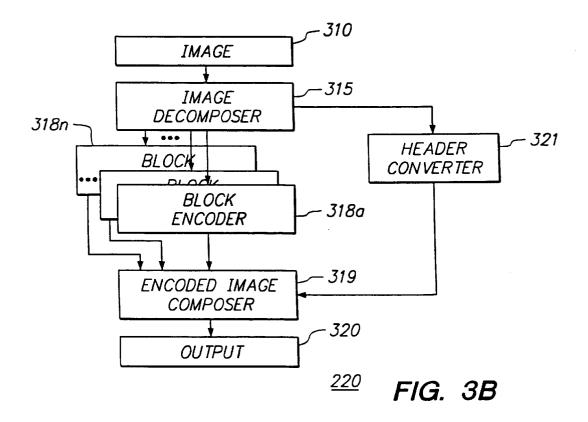

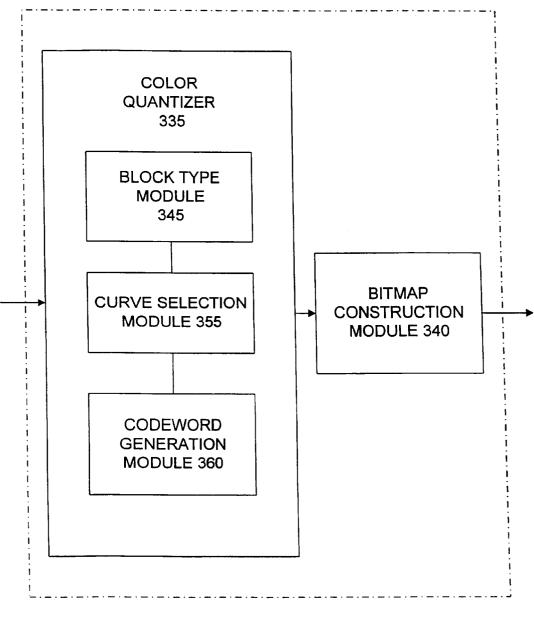

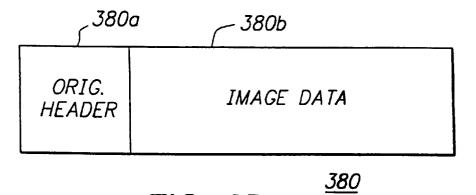

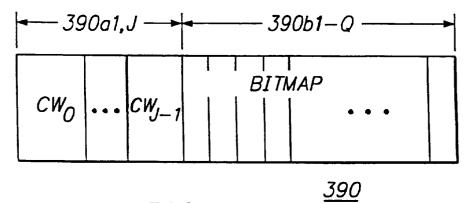

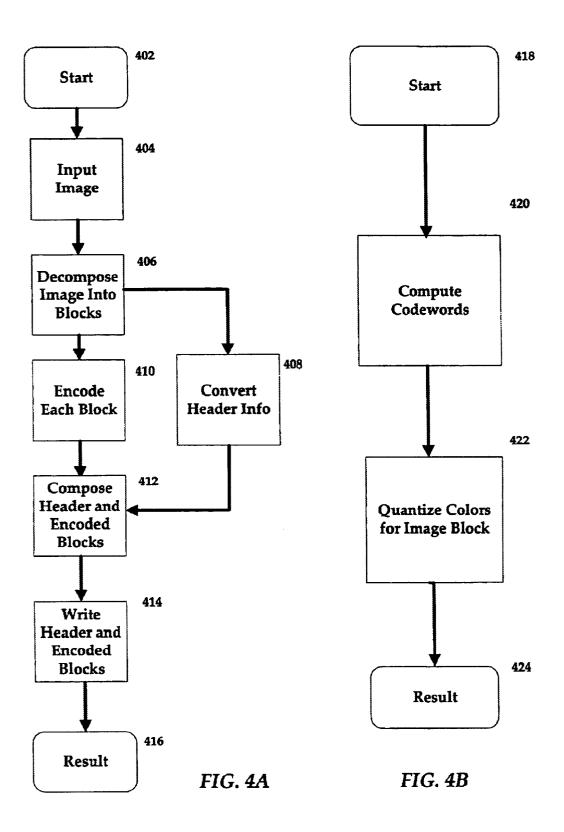

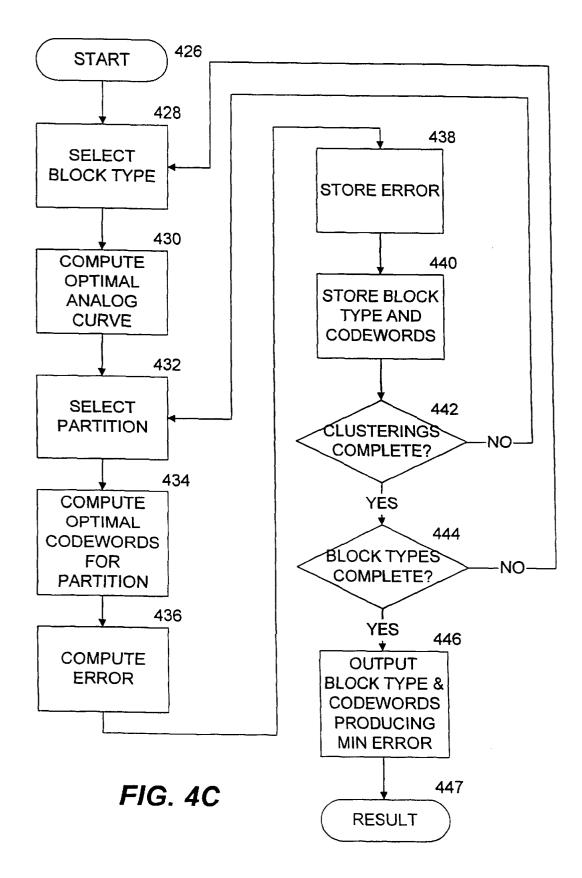

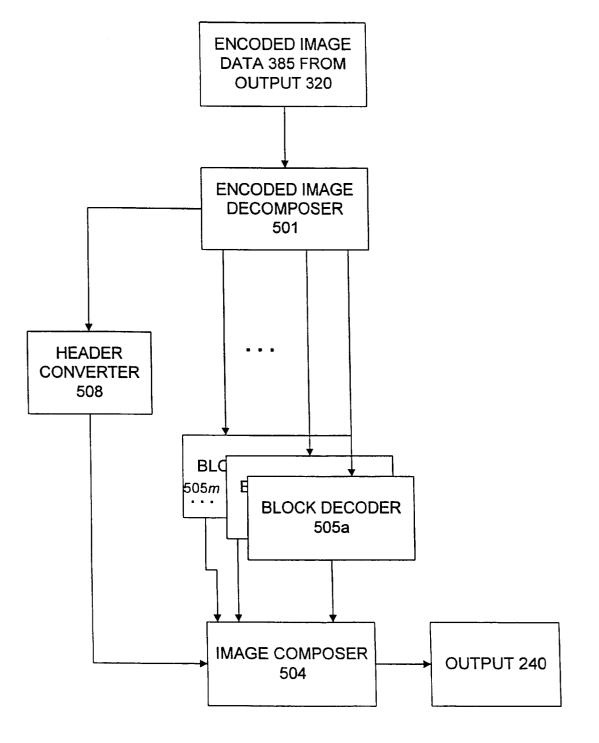

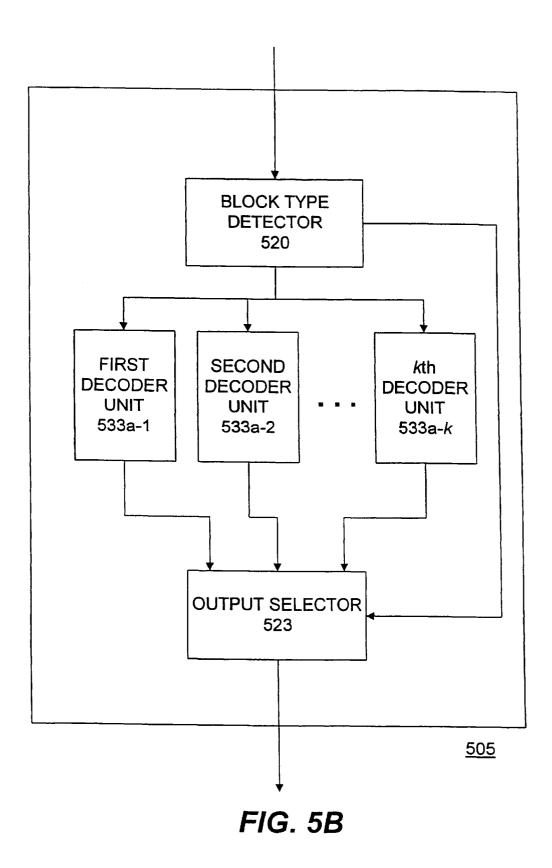

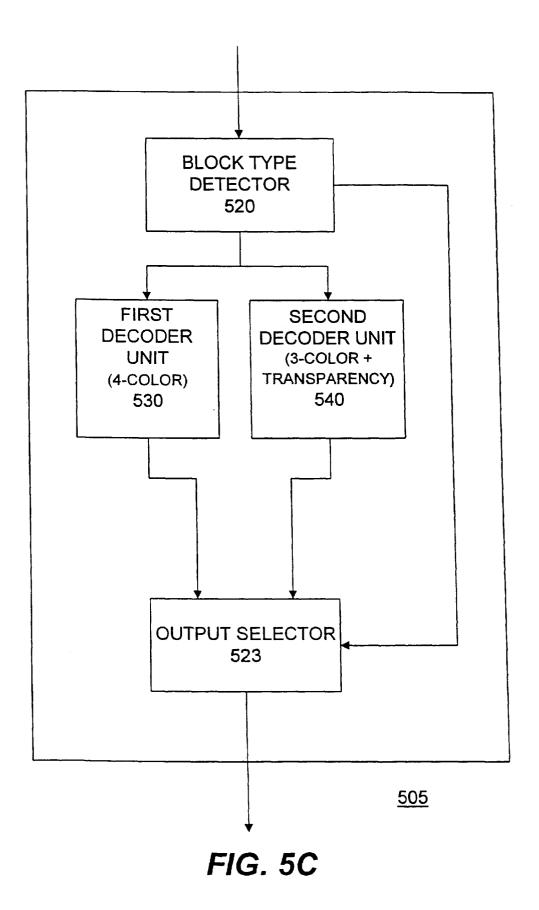

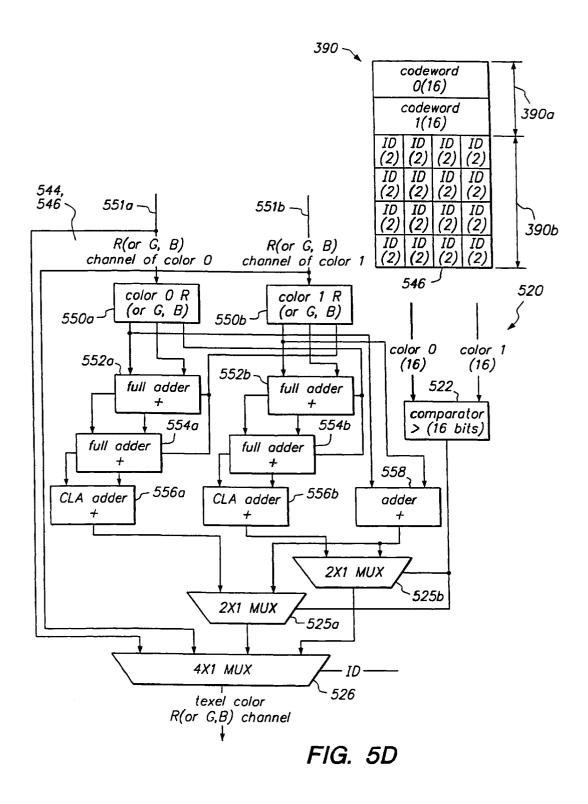

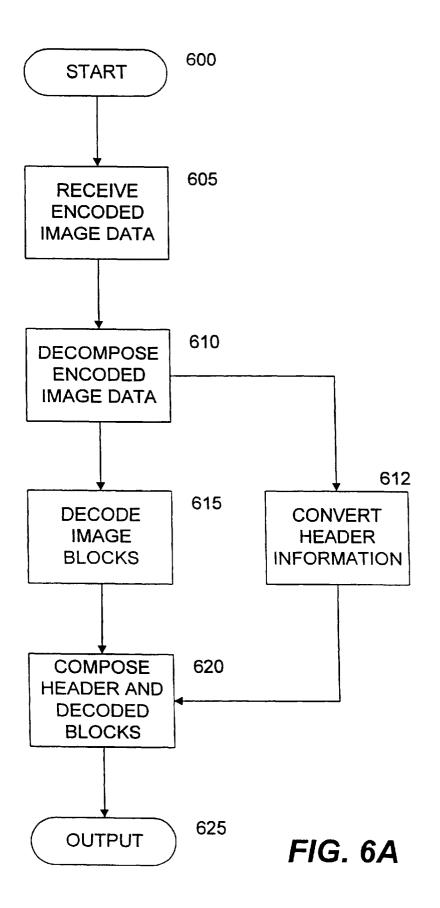

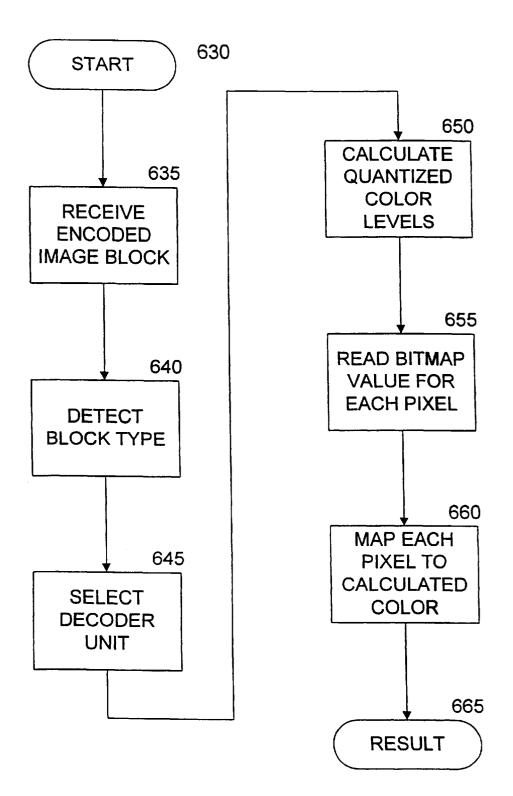

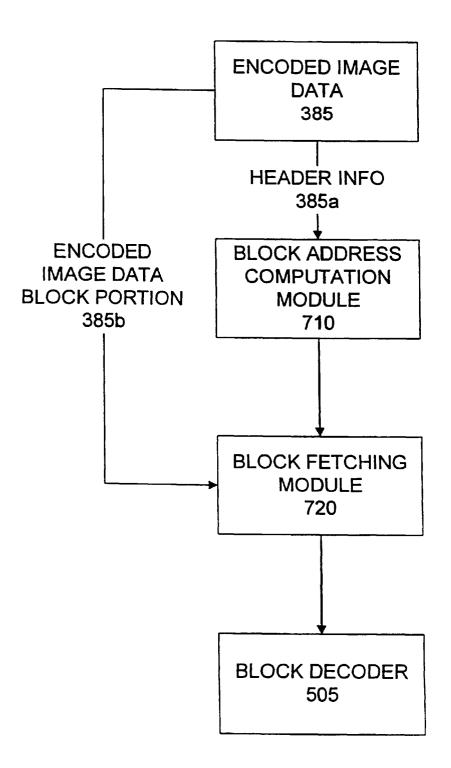

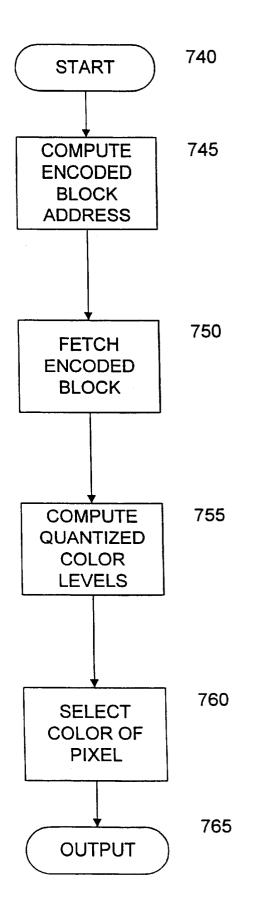

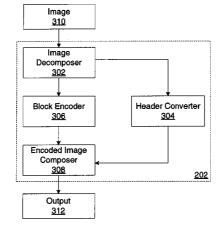

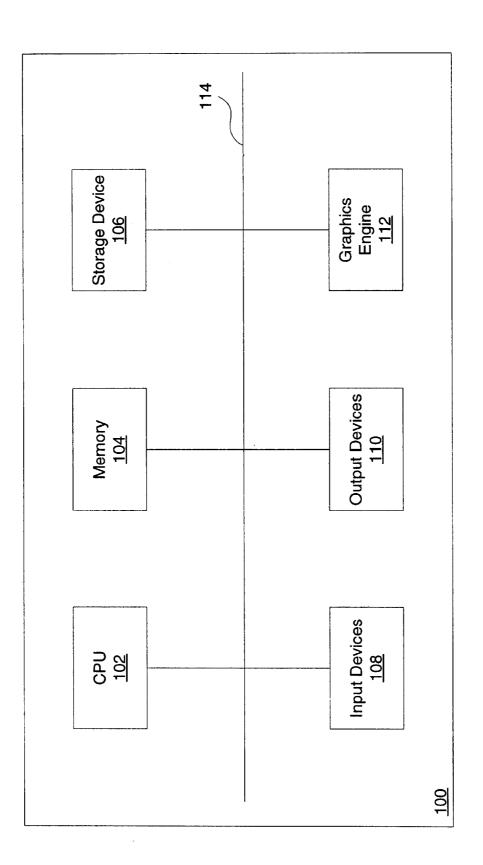

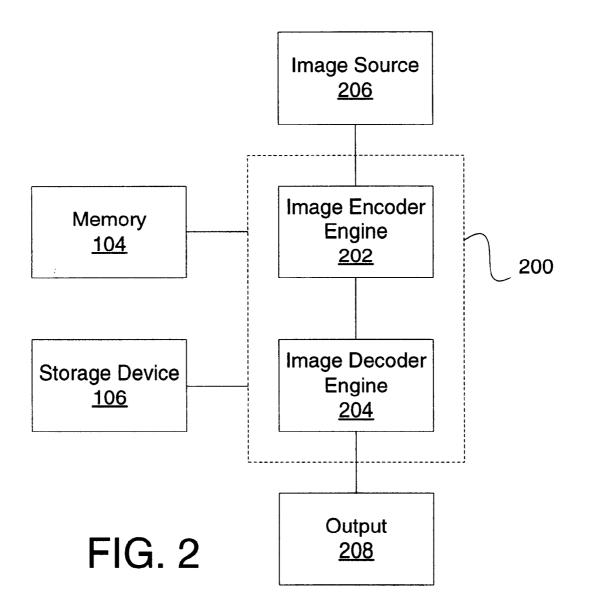

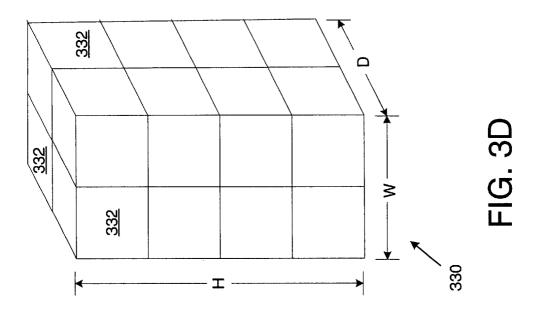

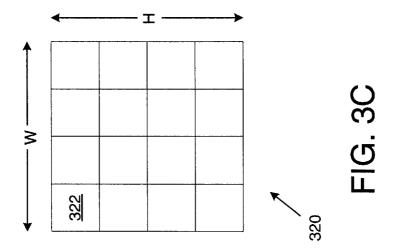

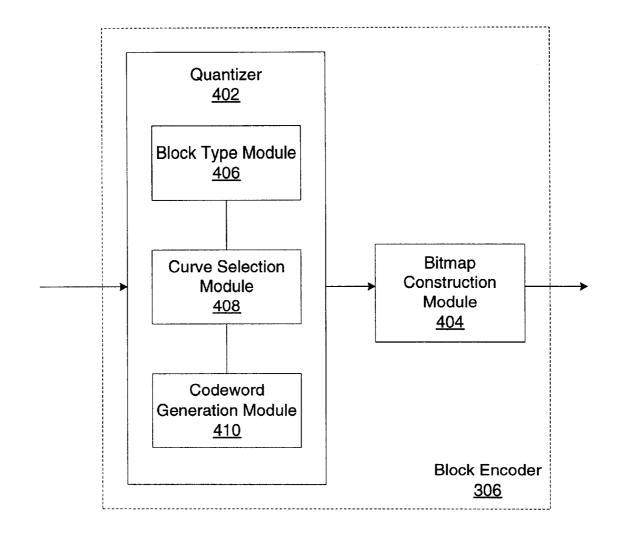

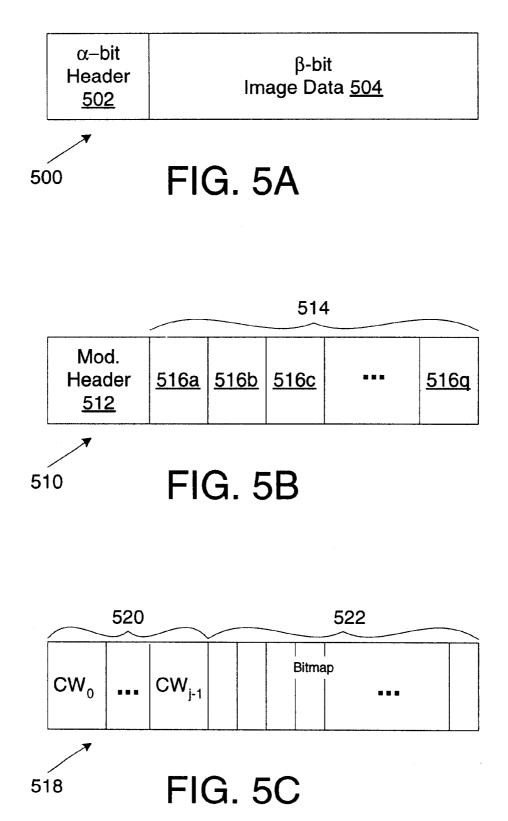

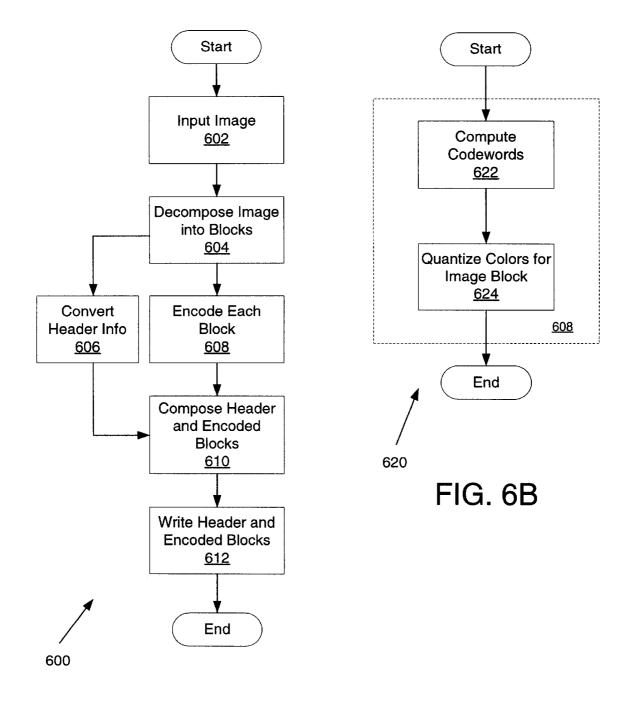

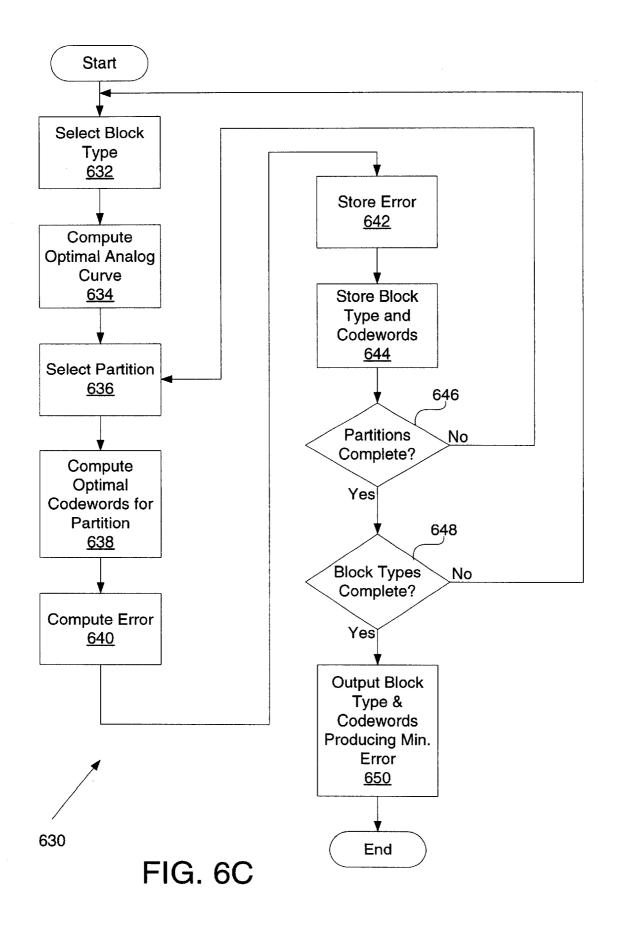

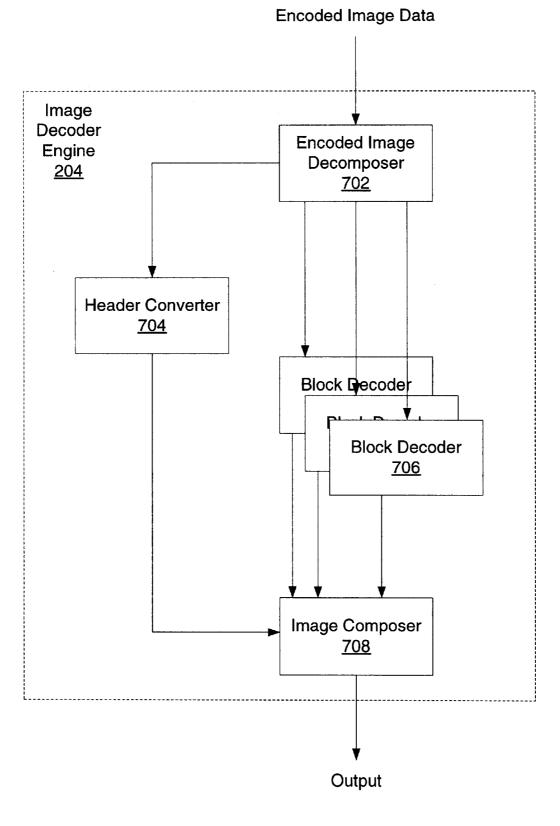

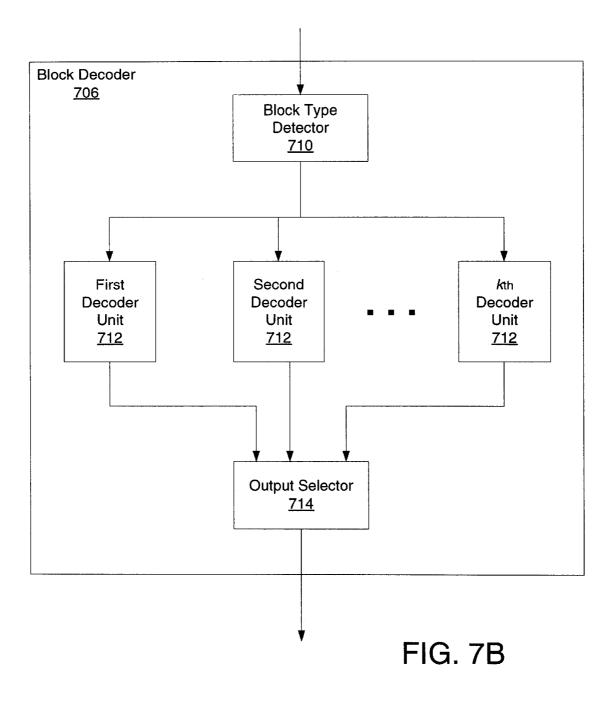

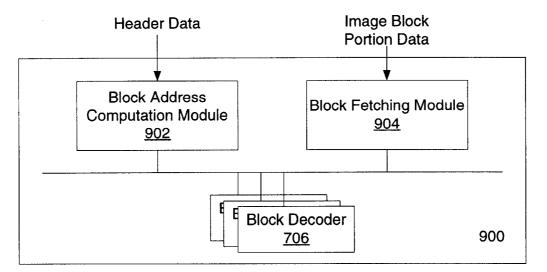

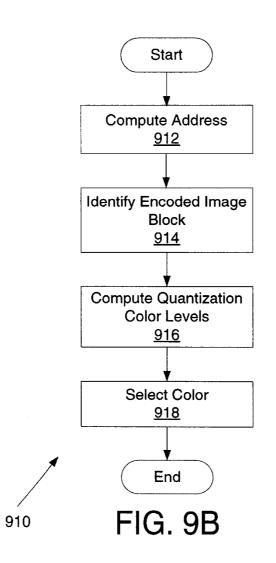

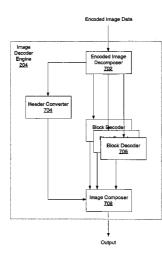

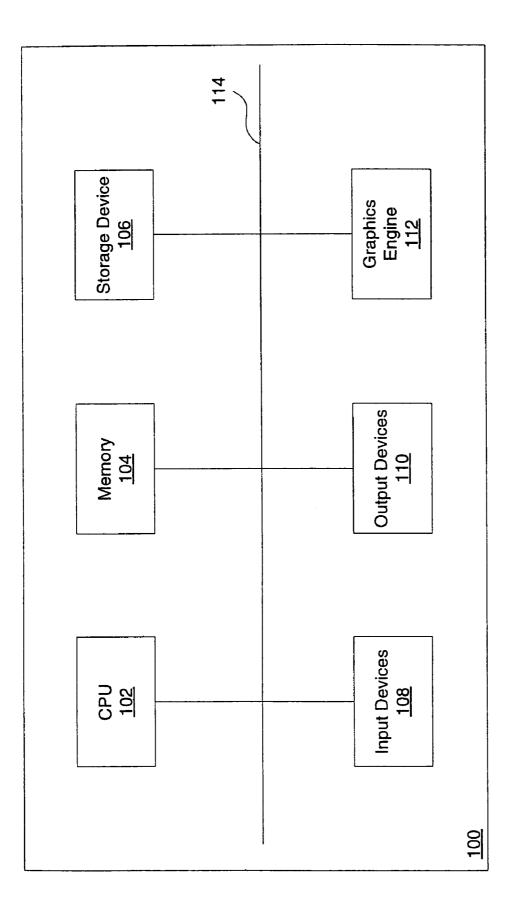

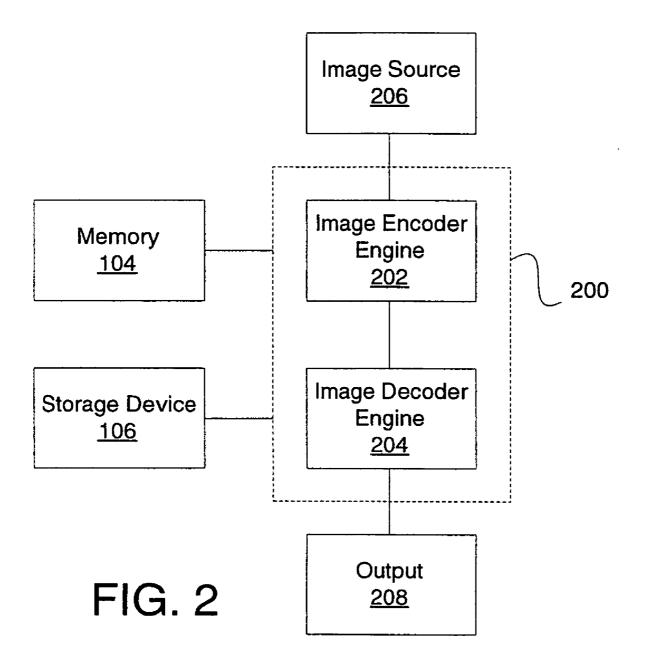

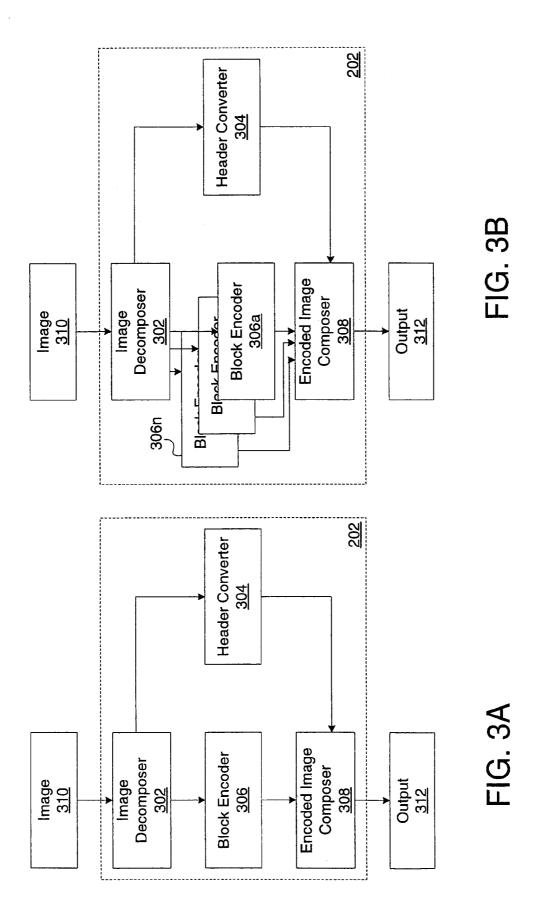

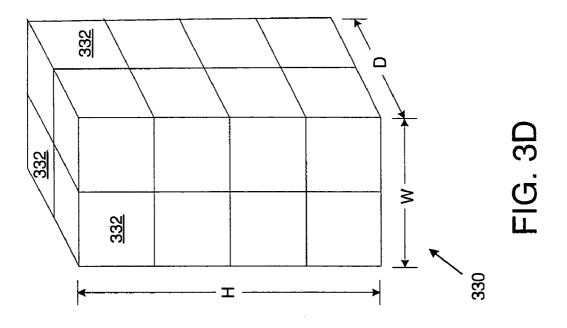

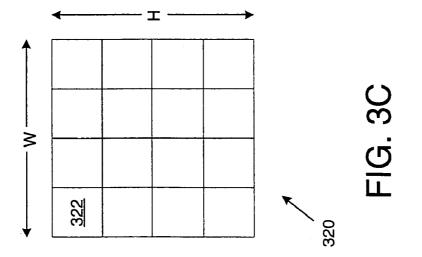

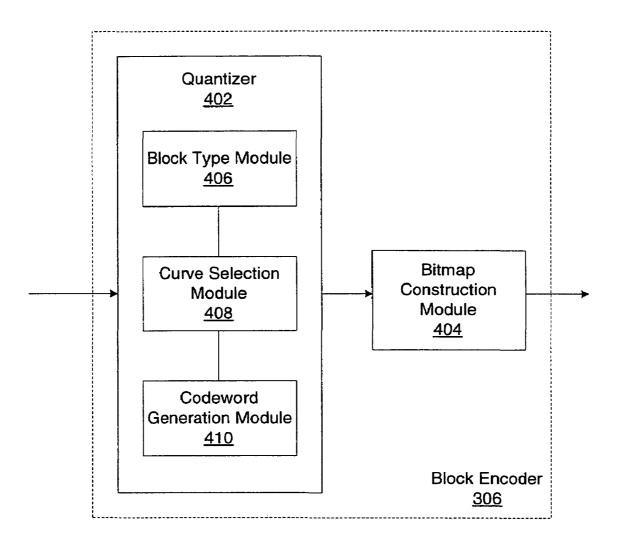

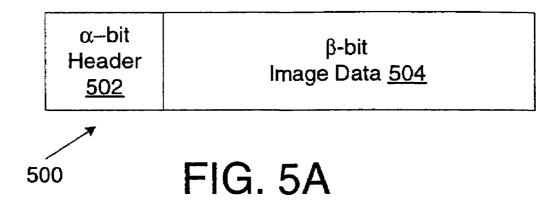

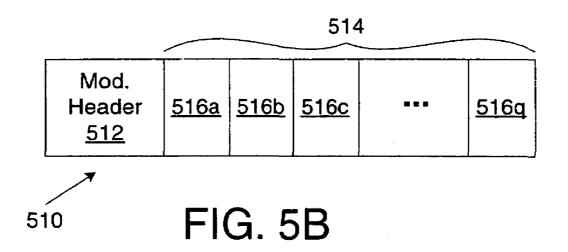

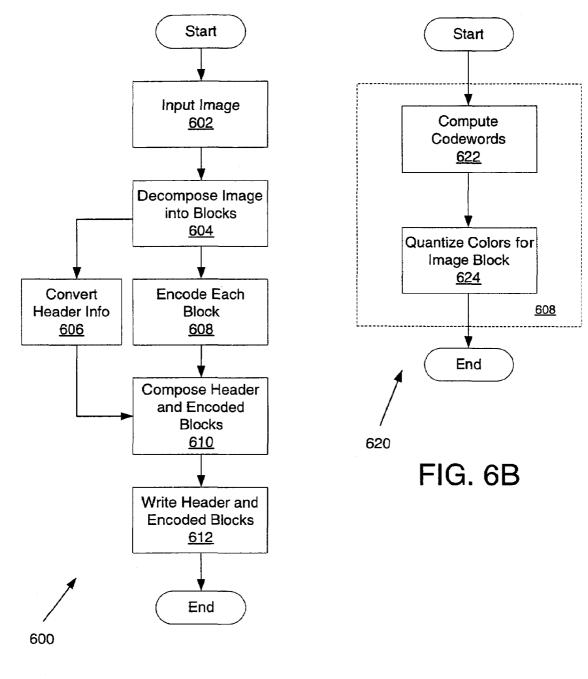

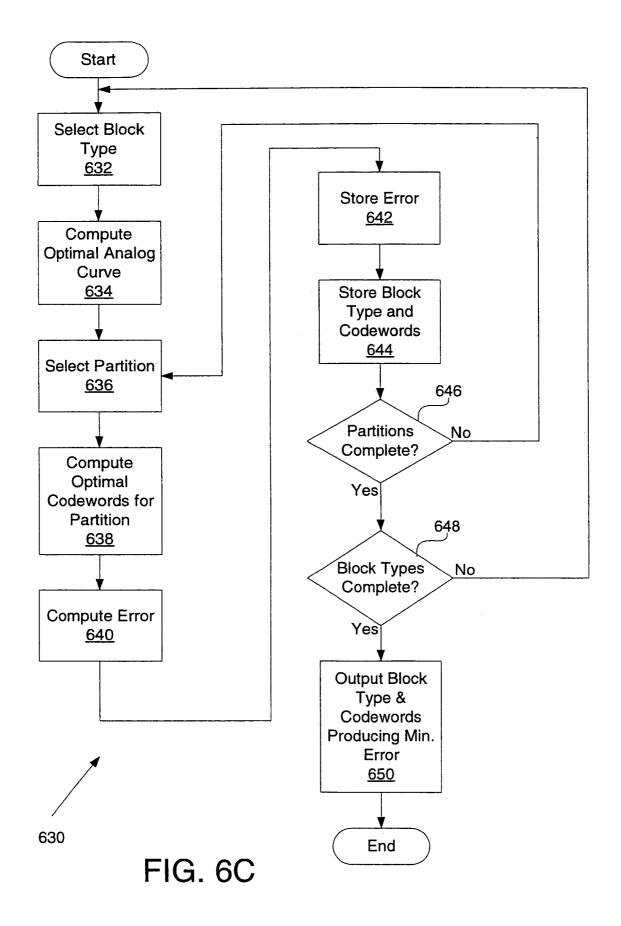

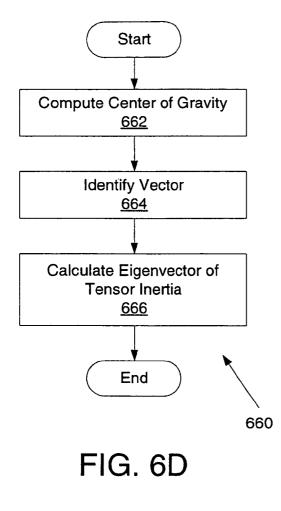

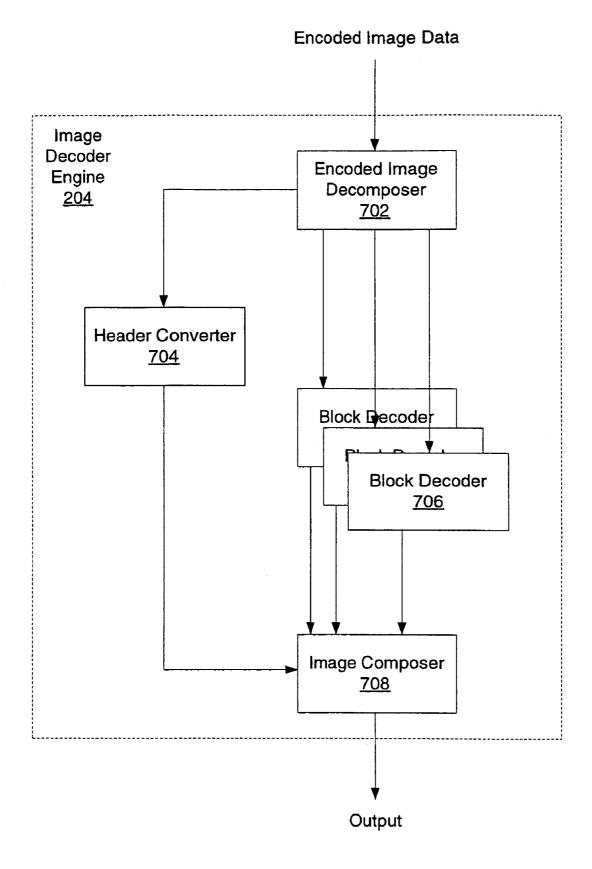

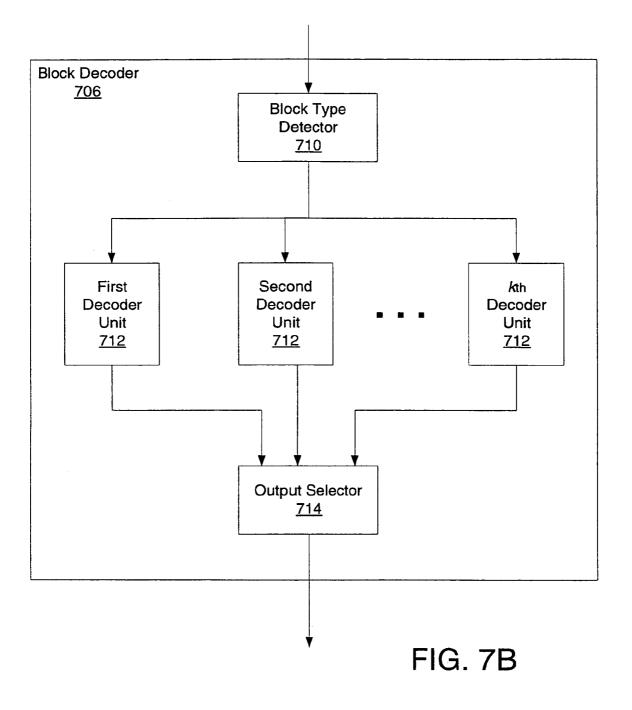

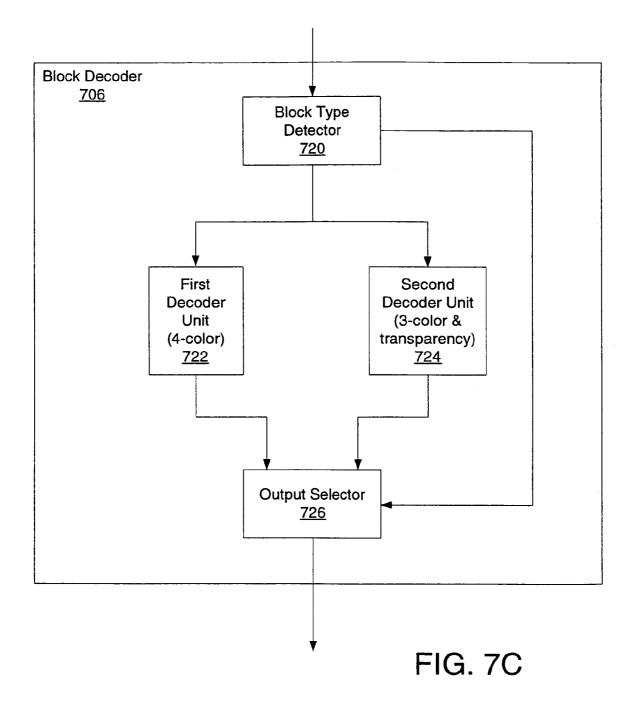

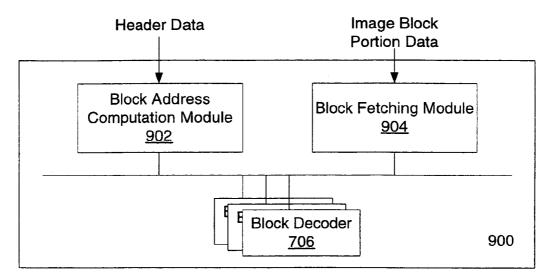

14. The Asserted Patents stem from the same parent application and are directed to

| 1  | various aspects of an image processing system involving compression and decompression of             |  |  |

|----|------------------------------------------------------------------------------------------------------|--|--|

| 2  | images. The '146, '978, and '417 Patents are all entitled "Fixed-Rate Block-Based Image              |  |  |

| 3  | Compression with Inferred Pixel Values."                                                             |  |  |

| 4  | 15. Apple designs and sells electronic devices, including the iPhone, iPod touch, iPad,              |  |  |

| 5  | and Mac computers. Apple also provides a software development kit ("SDK") that allows third          |  |  |

| 6  | party developers to design applications for its products.                                            |  |  |

| 7  | 16. As stated above, S3 Graphics has alleged in the ITC Complaint that Apple                         |  |  |

| 8  | infringes the Asserted Patents through the manufacture and distribution of certain hardware and      |  |  |

| 9  | software products.                                                                                   |  |  |

| 10 | 17. On June 25, 2010, the International Trade Commission instituted Investigation                    |  |  |

| 11 | No. 337-TA-724, styled In the Matter of Certain Electronic Devices with Image Processing             |  |  |

| 12 | Systems, Components Thereof, and Associated Software, to determine whether there is a violation      |  |  |

| 13 | of section 337 based on the allegations of the ITC Complaint.                                        |  |  |

| 14 | 18. In its Response to the ITC Complaint, Apple denied that there has been a violation               |  |  |

| 15 | of section 337. Apple further has asserted that the Asserted Patents are not infringed and are       |  |  |

| 16 | invalid.                                                                                             |  |  |

| 17 | 19. Therefore, at the present time, an actual controversy exists between Apple, on the               |  |  |

| 18 | one hand, and S3 Graphics, on the other, as to the validity of the Asserted Patents and the          |  |  |

| 19 | 9 infringement of those patents by Apple. This controversy is of such immediacy and reality as to    |  |  |

| 20 | warrant declaratory relief so that the parties may ascertain their rights and duties with respect to |  |  |

| 21 | the Asserted Patents.                                                                                |  |  |

| 22 | 20. An actual controversy also exists between Apple and S3 Graphics with respect to                  |  |  |

| 23 | patent licenses granted by S3 Graphics to third parties who supply components to Apple. Apple        |  |  |

| 24 | contends that these licenses bar S3 Graphics' assertions of infringement, but S3 Graphics has        |  |  |

| 25 | denied the existence of these licenses or denied that Apple is a beneficiary of them.                |  |  |

| 26 | <u>COUNT ONE</u>                                                                                     |  |  |

| 27 | Declaratory Judgment of Non-Infringement of the Asserted Patents                                     |  |  |

| 28 | 21. Apple realleges and incorporates herein by reference the allegations in paragraphs               |  |  |

|    | OHS West:261056792.3 - 3 - COMPLAINT                                                                 |  |  |

| 1  |                                                                                                      |  |  |

| 1  | 1 through 20 above.                                                                               |  |  |

|----|---------------------------------------------------------------------------------------------------|--|--|

| 2  | 22. S3 Graphics has alleged and continues to assert that Apple and its products                   |  |  |

| 3  | infringe the Asserted Patents.                                                                    |  |  |

| 4  | 23. Apple has not infringed and is not now infringing directly or indirectly, and has             |  |  |

| 5  | not induced or contributed to and is not now inducing or contributing to the infringement of, any |  |  |

| 6  | claim of the Asserted Patents, either literally or by application of the doctrine of equivalents. |  |  |

| 7  | 24. Apple seeks a declaratory judgment from this Court under Rule 57 of the Federal               |  |  |

| 8  | Rules of Civil Procedure and 28 U.S.C. § 2201 declaring that Apple is not infringing and has not  |  |  |

| 9  | infringed the Asserted Patents and granting Apple all other declaratory relief to which it may be |  |  |

| 10 | entitled.                                                                                         |  |  |

| 11 | COUNT TWO                                                                                         |  |  |

| 12 | Declaratory Judgment of Invalidity of the Asserted Patents                                        |  |  |

| 13 | 25. Apple realleges and incorporates herein by reference the allegations in paragraphs            |  |  |

| 14 | 1 through 24 above.                                                                               |  |  |

| 15 | 26. The claims of the Asserted Patents are invalid because they fail to comply with               |  |  |

| 16 | one or more requirements of the Patent Laws of the United States, including, but not limited to,  |  |  |

| 17 | 35 U.S.C. §§ 101, 102, 103, 112 and/or 116.                                                       |  |  |

| 18 | 27. Apple seeks a declaratory judgment from this Court under Rule 57 of the Federal               |  |  |

| 19 | Rules of Civil Procedure and 28 U.S.C. § 2201 declaring that the Asserted Patents are invalid and |  |  |

| 20 | granting Apple all other declaratory relief to which it maybe entitled.                           |  |  |

| 21 | PRAYER FOR RELIEF                                                                                 |  |  |

| 22 | WHEREFORE, Apple prays for judgment and relief as follows:                                        |  |  |

| 23 | 1. That Apple has not infringed, contributed to the infringement of, nor induced                  |  |  |

| 24 | infringement of any claim of the Asserted Patents;                                                |  |  |

| 25 | 2. That the claims of the Asserted Patents are invalid;                                           |  |  |

| 26 | 3. That this case is exceptional under 35 U.S.C. § 285;                                           |  |  |

| 27 | 4. For reasonable attorneys' fees pursuant to 35 U.S.C. § 285;                                    |  |  |

| 28 | 5. For further necessary or proper relief pursuant to 28 U.S.C. § 2202; and                       |  |  |

COMPLAINT

| 1  | 6. For such other relief as the Court deems just and proper. |                                       |  |

|----|--------------------------------------------------------------|---------------------------------------|--|

| 2  | DEMAND FOR JURY TRIAL                                        |                                       |  |

| 3  | Plaintiff hereby demands a jury trial in this action.        |                                       |  |

| 4  |                                                              |                                       |  |

| 5  | Dated: January 13, 2011                                      | ORRICK, HERRINGTON & SUTCLIFFE LLP    |  |

| 6  |                                                              | Vickie L. Feeman<br>Vickie L. Feeman  |  |

| 7  |                                                              | Vickie L. Feeman                      |  |

| 8  |                                                              | Attorneys for Plaintiff<br>APPLE INC. |  |

| 9  |                                                              |                                       |  |

| 10 |                                                              |                                       |  |

| 11 |                                                              |                                       |  |

| 12 |                                                              |                                       |  |

| 13 |                                                              |                                       |  |

| 14 |                                                              |                                       |  |

| 15 |                                                              |                                       |  |

| 16 |                                                              |                                       |  |

| 17 |                                                              |                                       |  |

| 18 |                                                              |                                       |  |

| 19 |                                                              |                                       |  |

| 20 |                                                              |                                       |  |

| 21 |                                                              |                                       |  |

| 22 |                                                              |                                       |  |

| 23 |                                                              |                                       |  |