| 1  | Perry J. Woodward, Esq. (State Bar No. 183876)<br>Michael Stebbins, Esq. (State Bar No. 138326) |                                                                                     |  |  |  |  |

|----|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|--|

| 2  | TERRA LAW, L.L.P.                                                                               | ORIGINAL                                                                            |  |  |  |  |

| 3  | 60 South Market Street, Suite 200<br>San Jose, California 95113-2333                            | FILED                                                                               |  |  |  |  |

| 4  | Tel: (408) 299-1200<br>Attorneys for Plaintiff                                                  | ADD 2 4 JUNE                                                                        |  |  |  |  |

| 5  | DYNETIX DESIGN SOLUTIONS, INC.                                                                  | RICHARD W. WIEKING<br>CLERK, U.S. DISTRICT COURT<br>NORTHERN DISTRICT OF CALIFORNIA |  |  |  |  |

| 6  | Of Counsel:<br>Edward W. Goldstein, Esq.                                                        | SAN JOSE                                                                            |  |  |  |  |

| 7  | Corby R. Vowell, Esq. GOLDSTEIN, FAUCETT & PREBEG, L.L.P.                                       |                                                                                     |  |  |  |  |

| 8  | 1177 West Loop South, Suite 400<br>Houston, Texas 77027                                         |                                                                                     |  |  |  |  |

|    | TEL: (713) 877-1515                                                                             |                                                                                     |  |  |  |  |

| 9  | FAX: (713) 877-1737                                                                             |                                                                                     |  |  |  |  |

| 10 | IN THE UNITED STAT                                                                              | ES DISTRICT COURT                                                                   |  |  |  |  |

| 11 | FOR THE NORTHERN DI                                                                             | STRICT OF CALIFORNIA                                                                |  |  |  |  |

| 12 | SAN JOSE                                                                                        | DIVISION                                                                            |  |  |  |  |

| 13 |                                                                                                 | CRE                                                                                 |  |  |  |  |

| 14 | DYNETIX DESIGN SOLUTIONS, INC.,                                                                 | Caso No.                                                                            |  |  |  |  |

| 15 | Plaintiff,                                                                                      | COMPLAINT AND DEMAND FOR JURY<br>TRIAL                                              |  |  |  |  |

| 16 | vs.                                                                                             |                                                                                     |  |  |  |  |

| 17 | AXIOM DESIGN AUTOMATION, INC.,                                                                  |                                                                                     |  |  |  |  |

| 18 |                                                                                                 |                                                                                     |  |  |  |  |

| 19 | Defendants.                                                                                     |                                                                                     |  |  |  |  |

| 20 | Plaintiff Dynetix Design Solutions, Inc.                                                        | ("Dynetix") brings this action against                                              |  |  |  |  |

| 21 | Defendant AXIOM Design Automation, Inc. (".                                                     | Axiom"), and for its cause of action alleges:                                       |  |  |  |  |

| 22 | The I                                                                                           | Parties                                                                             |  |  |  |  |

| 23 | 1                                                                                               | ed and existing under the laws of the State of                                      |  |  |  |  |

| 24 | California, with its principal place of business a                                              | nt 4448 Bangor Court, Dublin, California 94568.                                     |  |  |  |  |

| 25 | 2. Upon information and belief, Axiom is a corporation organized and existing                   |                                                                                     |  |  |  |  |

| 26 | under the laws of the State of California and is                                                |                                                                                     |  |  |  |  |

| 27 | elsewhere. Axiom may be served with process                                                     | by serving its registered agent Badru Agarwala                                      |  |  |  |  |

| 28 | at 7450 Foothill Road, Pleasanton, California                                                   | 94566.                                                                              |  |  |  |  |

|    | 1142802                                                                                         | 1                                                                                   |  |  |  |  |

|    | COMPLAINT AND DE                                                                                | MAND FOR JURY TRIAL                                                                 |  |  |  |  |

### Jurisdiction and Venue

3. This action arises under the patent laws of the United States, Title 35 United States Code, particularly §§ 271 and 281 and Title 28 United States Code, particularly §1338(a). Venue is proper in this Court under Title 28 United States Code §§ 1391(b) and (c) and 1400(b).

## **Intradistrict Assignment**

4. Assignment of this action to the San Jose Division of the Northern District of California is in conformity with Civil Local Rule 3-2(c). A substantial part of the events which give rise to this action occurred at Defendant's principal place of business in Milpitas, California.

## **Claim For Patent Infringement**

- 5. On October 15, 2002, U.S. Patent No. 6,466,898 ("the '898 patent") was duly and legally issued for "Multithreaded Mixed Hardware Description Languages Logic Simulation on Engineering Workstations." A copy of the '898 patent is attached as Exhibit A and is made a part hereof. By assignment, Dynetix is the owner of the '898 patent and at all relevant times has had the right to enforce the '898 patent.

- 6. The '898 patent, in general, relates to electronic design automation and simulation systems for integrated circuits. More specifically, the '898 patent relates to multithreaded logic simulation systems that are capable of processing design files coded in a plurality of hardware description languages (HDLs).

- 7. Upon information and belief, Axiom provides multithreaded simulation systems for processing design files coded in a plurality of different HDLs, including but not limited to the MPSim product. By providing such products, Axiom has in the past and continues to infringe directly, by inducement, or by contributing to the infringement of the '898 patent, including but not limited to claims 1, 5, 6 and 7.

- 8. As a result of Defendant's infringing conduct, the Defendant has damaged Dynetix. Axiom is liable to Dynetix in an amount that adequately compensates Dynetix for Axiom's infringement, which by law in no event can be less than a reasonable royalty.

- 9. As a consequence of the Defendant's infringement, Dynetix has been irreparably damaged and such damage will continue without the issuance of an injunction by this Court.

#### **Demand for Jury Trial** 1 Dynetix demands a jury trial on all claims and issues. 10. 2 **Prayer For Relief** 3 WHEREFORE, Dynetix prays for entry of judgment: 4 That claim 1 of U.S. Patent 6,466,898 has been infringed by the Defendant and 5 1. by others whose infringement has been contributed to and/or induced by Defendant; 6 That Defendant and each of its officers, agents, employees, representatives, 2. 7 successors, assigns and those acting in privity or concert with them be permanently enjoined 8 from further infringement of U.S. Patent 6,466,898. 9 That Defendant account for and pay to Dynetix all damages and costs caused by 3. 10 Defendant's activities complained of herein; 11 That Dynetix be granted pre-judgment and post-judgment interest on the 4. 12 damages caused by reason of Defendant's activity complained of herein; 13 That Dynetix be granted its attorneys' fees in this action; 5. 14 That costs be awarded to Dynetix; and 6. 15 That Dynetix be granted such other and further relief that is just and proper 7. 16 under the circumstances. 17 TEKRA LAW, LLP Dated: April 24, 2006 18 19 20 Perry Woodward TERKA LAW LLP 21 60 South Market Street, Suite 200 San Jose, CA 95113 22 Tel: 408/288-7325 Fax: 408/998-4895 23 ATTORNEYS FOR PLAINTIFF DYNETIX DESIGN SOLUTIONS, INC. 24 Of Counsel: Edward W. Goldstein 25 Corby R. Vowell GOLDSTEIN, FAUCETT & PREBEG, L.L.P. 26 1177 West Loop South, Suite 400 Houston, Texas 77027 27 (713) 877-1515 – Telephone (713) 877-1737 - Facsimile 28 1142802

COMPLAINT AND DEMAND FOR JURY TRIAL

# (12) United States Patent Chan

(10) Patent No.: US 6,466,898 B1

(45) Date of Patent: Oct. 15, 2002

# (54) MULTITHREADED, MIXED HARDWARE DESCRIPTION LANGUAGES LOGIC SIMULATION ON ENGINEERING WORKSTATIONS

(76) Inventor: Terence Chan, 15 Macpherson Pl.,

Danville, CA (US) 94526

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 09/229,134

- (22) Filed: Jan. 12, 1999

| (51) | Int. Cl.'       | Guor 17/50                   |

|------|-----------------|------------------------------|

| (52) | U.S. Cl         | 703/17; 703/16; 703/14;      |

| ` ,  | 703/15; 703/19; | 703/20; 716/6; 716/2; 716/3; |

|      | . ,             | 716/18; 716/16               |

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,732,247 A | * | 3/1998  | Dearth et al    | 716/18 |

|-------------|---|---------|-----------------|--------|

| 5,774,368 A | * | 6/1998  | Chen et al      | 716/18 |

| 5,857,091 A | • | 1/1999  | Fernandes et al | 716/18 |

| 5,870,588 A |   | 2/1999  | Rompaey et al   | 716/18 |

|             |   |         | Kasuya          |        |

| 5.999.734 A | * | 12/1999 | Willis et al    | 716/18 |

| 6,152,612 A | * | 11/2000 | Liao et al      | 716/18 |

| 6,212,667 B1 * | 4/2001 | Geer et al 716/6   |

|----------------|--------|--------------------|

| 6,226,780 B1 * | 5/2001 | Bahra et al 716/18 |

| 6,230,307 B1 * | 5/2001 | Davis et al 716/16 |

| 6,263,483 B1 * | 7/2001 | Dupenloup 716/18   |

#### OTHER PUBLICATIONS

- "A Portable Mechanism for Vectorizing Compiled Event-Driven Simulation", Mittra., IEEE, 1997.\*

- "A Hierarchical Compiled Code Event-Driven Logic Simulator", Lewis, IEEE, 1991.\*

- "An Efficient Strategy for Developing a Simulator for a Novel Concurrent Multithreaded Processor Architecture", Jian Huang et al., IEEE, Jul. 1998.\*

- \* cited by examiner

Primary Examiner—Hugh M. Jones

Assistant Examiner—William Thomson

(74) Attorney, Agent, or Firm—Chi Ping Chang; Pacific

Law Group LLP

#### (57) ABSTRACT

This invention describes a multithread HDL logic simulator that is unique from the prior arts. Specifically, it can process both VHDL and Verilog languages in a single program, and it uses special concurrent algorithms to accelerate the tool's performance on multiprocessor platforms to achieve linear to super-linear scalability on multiprocessor systems. Furthermore, the invention includes a unique remote logic simulation and job scheduling capabilities.

#### 59 Claims, 16 Drawing Sheets

Oct. 15, 2002

Sheet 1 of 16

Figure 1

Figure 2

Oct. 15, 2002

Sheet 2 of 16

Figure 3

Oct. 15, 2002

Sheet 3 of 16

Figure 5

U.S. Patent Oct. 15, 2002 Sheet 4 of 16

| File | View       | Radix Time |       |    |    |  |

|------|------------|------------|-------|----|----|--|

| Time | <b>I</b> 1 | 12         | 01    | 02 | ж1 |  |

| 0.0  | 1          | 0          | 10101 | 0  | 0  |  |

| 8.0  | 1          | 1          | 10101 | 0  | 0  |  |

| 8.0  | 1          | 1          | 10101 | 0  | 0  |  |

| 9.0  | 0          | 1          | 11111 | 0  | 1  |  |

| 12.0 | 0          | 0          | 11111 | 0  | 1  |  |

| 19.0 | 0          | 1          | 11111 | 0  | 1  |  |

| 21.0 | 0          | 0          | 11111 | 0  | 1  |  |

Figure 6

Oct. 15, 2002

Sheet 5 of 16

Figure 7

Oct. 15, 2002

Sheet 6 of 16

Figure 8

Oct. 15, 2002

Sheet 7 of 16

US 6,466,898 B1

# Clocks specification for ckt. LFSR100K

CLK; # use clock period defined in HDL file CLK2 1/15 0/20; # clock period = 35 CLK3 1/10 0/5 1/15 0/20; # multi-phase clock

# define these for mixed event-driven and cycle-based simulation # Cycle = ( CLK, L1, L2 );

Figure 10

Oct. 15, 2002

Sheet 8 of 16

Figure 11

**U.S. Patent** Oct. 15, 2002

Sheet 9 of 16

Figure 12

| Job Name: [      |   |        |            |  |

|------------------|---|--------|------------|--|

| Target host:     |   |        | Directory: |  |

| Compile Files: [ |   |        | Add        |  |

| Simulation: [    |   |        | Delete     |  |

| Schedules: [     |   |        |            |  |

| Emails [         |   |        | Commands:  |  |

| O                | K | Cancel | Help       |  |

Figure 13

## **U.S. Patent** Oct. 15, 2002

Sheet 10 of 16

US 6,466,898 B1

Figure 14

H - per-thread specific heap memory Legend:

E - per-thread specific event queue

F - per-thread specific fanut queue

Figure 15

Oct. 15, 2002

**Sheet 11 of 16**

Figure 16

Oct. 15, 2002

Sheet 12 of 16

Figure 17

Oct. 15, 2002

**Sheet 13 of 16**

US 6,466,898 B1

Figure 19

Oct. 15, 2002

**Sheet 14 of 16**

Figure 20

Oct. 15, 2002

**Sheet 15 of 16**

Figure 21

| Time (ns) | I1 | 12 | 01    | 02 | <b>x</b> 1 |

|-----------|----|----|-------|----|------------|

| 0.0       | 1  | 0  | 10101 | 0  | 0          |

| 8.0       | 1  | 1  | 10101 | 0  | 0          |

| 8.0       | 1  | 1  | 10101 | 0  | 0          |

| 9.0       | 0  | 1  | 11111 | 0  | 1          |

| 12.0      | 0  | 0  | 11111 | 0  | 1          |

| 19.0      | 0  | 1  | 11111 | 0  | 1          |

| 21.0      | 0  | 0  | 11111 | 0  | 1          |

Figure 22

**U.S. Patent** Oct. 15, 2002

**Sheet 16 of 16**

Figure 23

#### US 6,466,898 B1

#### MULTITHREADED, MIXED HARDWARE DESCRIPTION LANGUAGES LOGIC SIMULATION ON ENGINEERING WORKSTATIONS

#### BACKGROUND OF THE INVENTION

Logic simulator is an essential electronic design automation (EDA) tool to facilitate the design and debug of very large scale integrated (VLSI) circuit. Examples of these VLSI designs include microprocessors for personal computers and workstations, micro-controllers for embedded systems, and internetworking routers and switches, etc. The VLSI circuit designers use logic simulators to simulate and verify the functional behavior and timing characteristics of their circuit designs on their engineering workstations before committing such designs to fabrication. The benefits of the logic simulators are to reduce new product development time and costs, and to improve engineer productivity and product quality.

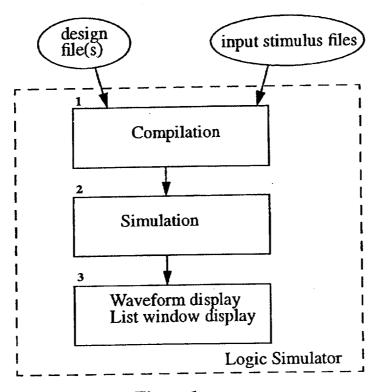

Referring to FIG. 1, the operations of a logic simulator is depicted. Specifically, a user's inputs to a logic simulator are one or more text files, which describe the specification of his circuit. These design files are usually coded in a hardware description language (HDL). In addition, the user also provides an input stimulus file to the simulator. This file may consist of input vectors to be applied to the circuit at specified time intervals, and/or some behavioral HDL code that describes how various signals (i.e., clocks and global reset signals) in the circuits are to change states during the simulation.

The logic simulator compiles the design files and stimulus file supplied by the user into a database. It may flag any errors it detects in the design files or stimulus file. These errors may include syntax errors, undefined library cells, 35 signals with no driver and/or receivers, and bus contentions, etc. After the input files are successfully compiled, the logic simulator applies input stimulus to the circuit and performs simulation of the circuit for the duration of time as specified by the user. During simulation, the simulator also keeps 40 track of the changes of states of any user-selected signals in the design. At the completion of the simulation, the simulator will bring up a graphical waveform window or a tabular state-listing window to show the user the selected signal states for the entire simulation run.

There are two types of logic simulators being widely used namely, event-driven logic simulator and cycle-based logic simulator. The event-driven logic simulators are the traditional simulators, which model both the functional and timing behaviors of user circuits. They can be applied for 50 any type of digital designs. The cycle-based simulator, on the other hand, models only the functional behaviors of user designs. Thus, a cycle-based simulator runs faster (up to 10 time or more) than an event-driven simulator, but it does not provide timing verification of user designs and is suitable 55 only for synchronous designs (synchronous designs are those that one or more master clocks controlling all activities in the designs)

In the 1980s to early 1990s, most EDA vendors offered event-driven logic simulators running on either UNIX-based 60 workstations or Windows-based personal computers. However, as VLSI designs get larger and more complex, the time to perform simulation on those general-purpose workstations and personal computers grew exponentially. To offering cycle-based simulators to allow users, at their own elections, to trade-off accuracy with speed. Users who use

cycle-based simulators must also use a separate tool (e.g., a static timing analyzer) to verify the correctness of the timing characters of their designs.

Besides offering cycle-based simulators, some EDA vendors have introduced hardware-accelerators or hardware emulators to speed up the simulation of large designs. Specifically, a hardware accelerator hardwires the logic simulation algorithm into hardware, so that it can speedup the simulation of any given design by 10 to 100 times. A hardware emulator, on the other hand, programs a group of field-programmable gate array (FPGA) chips to emulate the logic functions of a given design, and it "simulates" the designs in real hardware speed. A hardware emulator can speedup simulation by a 1000 times or more. The drawback of the hardware accelerators and hardware emulators are that they are very expansive and designers can use them only on a time-sharing basis. Thus, they are mostly used as regression testing tools and not a debug tool. Furthermore, since they do not accurately model timing characteristic of user designs, the users still need to use other tools, like a static timing analyzer, to verify the timing behavior of their circuits separately.

With the recent introduction of multiprocessor workstations (UNIX-based and Windows™-based), some EDA vendors have realized that they can accelerate their tools performance by porting their applications onto such workstations. By using multiple microprocessors (CPUs) concurrently on these workstations, the performance of their tools can rival that of hardware accelerators and emulators, while still provides all the benefits of a traditional logic simulator. Furthermore, the multiprocessor workstations cost much less (i.e., ten to hundred times less) than that of hardware accelerators and emulators, and can be used for other engineering services in addition to logic simulation (e.g., act as file servers or electronic mail servers). Thus, use of multiprocessor workstations in VLSI design houses seems to be the future trend in the industry.

EDA tools that employ multiple CPUs on a single workstation to accelerate their performance are said to be multithreaded. Specifically, a thread is a process flow in a program that runs on a CPU. If a program can have multiple threads executing on multiple CPUs concurrently, then its is a multithreaded applications. Most EDA applications available today are single-threaded, which means that those applications performance on a multiprocessor system is still the same as that running on a single system.

Most VLSI designers use a hardware description language (HDL) to write their designs. The most commonly used hardware description languages are VHDL (VHSIC Hardware Description Language, where VHSIC stands for Very High Speed Integrated Circuit) and Verilog. They are standardized by the IEEE (Institute of Electrical and Electronic Engineering) society, and are widely supported by the electronics and semiconductor industries around the world. Most commercial logic simulators support either VHDL or Verilog language. A few EDA vendors provide a simulation backplane to interconnect a VHDL and a Verilog simulator, so that a user can simulate his VLSI design coded in both VHDL and Verilog. These products are not very popular as they are expensive (i.e., users need to purchase two separate simulators and the backplane) and inefficient in their performance.

Referring to Table 1, it lists the major commercial HDL reduce the design verification time, many EDA vendors are 65 logic simulators, their features and the HDL languages they supported. There are currently three EDA vendors that sell multithreaded logic simulators. Synopsys Incorporated sells

#### US 6,466,898 B1

a multithreaded event-driven logic simulator on UNIX platforms; QuickTurn Design Systems and Avanti Corporation offer multithreaded cycle-based logic simulators on UNIX platforms. It is noted, however, none of these vendors offers any multithreaded logic simulators that support the multiprocessor Linux and Windows™ platforms. In addition, It should be further noted there is no commercial logic simulator that supports both the VHDL and Verilog languages, and is also multithreaded.

There is therefore an apparent need for a general-purpose 10 multithreaded logic simulator that supports both the VHDL and Verilog languages in a single program to perform both a event-driven and a cycle-based logic simulation on a multiprocessor platform chosen by a user. There is a further need that such general-purpose multithreaded logic simulator can support both the local and remote users through its network resources.

Accordingly, one object of the invention is to provide for a new multithreaded logic simulator that uses unique algorithms to achieve excellent performance on multi-CPU platforms (e.g., UNIX, Linux, and Windows™), and yet <sup>20</sup> supports both the VHDL and Verilog languages in a single program such that the simulator can be used in any HDL design environments. The users do not need to maintain expensive workstations or separate VHDL and Verilog simulators to reduce product development costs.

Another object of the invention is to provide for a logic simulator that allows users to learn only one single simulator and yet be able to code their HDL designs in either VHDL and/or Verilog, which can be subsequently verified on any of the UNIX, Linux, or Windows<sup>TM</sup> platforms, to improve 30 users' engineering productivity and shorten product development time and costs.

One more object of the invention is to provide for a logic simulator that allows users to easily import any design source files (e.g., intellectual property core logic design) from any third party design house and simulate such design source files with their own design regardless whether the third party design files are coded in the users' own HDL languages or not to further improve engineering productivity and to shorten product development time and costs.

Still one object of the invention is to provide for a unique new network-based simulation method to facilitate VLSI designers to make full use of their network resources to perform logic simulation. Specifically, the VLSI designers can treat all their networked (single- or multi-processor) 45 machines as one giant computer, and to perform compilation and simulation of their designs on their local desktop computers or any other computers on the network. This method not only improves users' engineering productivity, but also improves the return of investment of users' hardware and software resources. This new method is not described or implemented in any prior arts

In addition to all the above, one more object of the invention is to provide for a logic simulator that provides a simulation job scheduling method which allows users to schedule compilation and simulation of their designs on any remote or local (single- or multi-processor) machines, at their specified time(s). This feature allows large design groups to schedule and balance the workload of their network machines, as well as to define periodic regression testing of their VLSI designs. The job-scheduling feature is 60 not described or implemented in any prior arts. As described above, this feature provides further benefits to improve users' engineering productivity as well as to users' return of hardware and software investments.

Finally, another object of the invention is to provide for a 65 and the input of data to the logic simulator from a user; logic simulator whose multithreaded capability allows users to reduce drastically their simulation time on multiprocessor

platforms to reduce development costs and time, and to improve engineering productivity and product quality.

#### SUMMAY OF THE INVENTION

This invention describes a novel concurrent, multithreaded algorithm to accelerate the execution of logic simulation of HDL (VHDL and/or Verilog) designs on any general-purpose multi-processor computer systems including, but without limitation to, UNIX, Linux, and Windows™ platforms. The algorithm enables the logic simulator provided by the invention to achieve a scalable performance (i.e., from linear to super-linear) according to the number of CPUs on the selected platform.

This invention describes further a novel HDL logic simulator that supports both VHDL and Verilog HDL design languages in a single program, and is multithreaded on any platforms. These features allow VLSI chip and/or system designers to mix-and-match their HDL designs (Verilog and/or VHDL) and run simulation on any hardware resources they have available.

One aspect of the invention is to provide for a novel HDL simulator that provides seamless access of network resources for HDL design compilation and simulation. Specifically, by installing a server program which runs on any of the remote workstations including, but without limitation to, UNIX, Linux, or Windows<sup>TM</sup>, users can access design files on any of such machines directly from their respective computers, via a user-interface ("UI" or "UIs") program(s). Furthermore, the users can instruct (via their local UIs) remote servers to compile and/or simulate HDL designs on the server hosts. The remote compilation and/or simulation results are automatically transferred back to the user' local hosts and are displayed on their UIs.

Another aspect of the invention is to provide for a novel HDL simulator to provide simulation job scheduling on local and/or remote platforms including, but not limited to, UNIX, Linux, and Windows™. This features allow VLSI designers to balance the work loads on their network resources by scheduling simulation runs at off-peak hours, as well as to automate the regular regression testing of their designs.

TABLE 1

|   | The Commercial Logic Simulators and their Properties |           |                |                  |     |       |  |  |  |  |

|---|------------------------------------------------------|-----------|----------------|------------------|-----|-------|--|--|--|--|

|   | Product                                              | Vendor    | HDL language   | Platforms        | МТ  | Sim   |  |  |  |  |

| 5 | VCS                                                  | Synposys  | Verilog        | UNIX,<br>Windows | No  | Event |  |  |  |  |

|   | vss                                                  | Synopsys  | VHDL           | UNIX,<br>Windows | No  | Event |  |  |  |  |

|   | Cyclon                                               | Synopsys  | VHDL           | UNIX,<br>Windows | No  | Cycle |  |  |  |  |

| 0 | SpeedSim-MT                                          | Synopsys  | VHDL           | UNIX             | Yes | Event |  |  |  |  |

|   | LeapFrog                                             | Cadence   | VHDL           | UNIX,<br>Windows | No  | Event |  |  |  |  |

|   | Verilog-XL                                           | Cadence   | Verilog        | UNIX             | No  | Event |  |  |  |  |

|   | Polaris                                              | Avanti    | Verilog        | UNIX             | Yes | Cycle |  |  |  |  |

|   | SpeedWave                                            | Quickturn | Verilog        | UNIX             | Yes | Cycle |  |  |  |  |

| 5 | QuickHDL                                             | Mentor    | VHDL & Verilog | UNIX,<br>Windows | No  | Event |  |  |  |  |

Legend:

Event = Event-driven simulation.

Cycle - Cycle-based simulation

MT = multithreaded kernal.

Sim = simulation method

#### BRIEF DESCRIPTION OF THE FIGURES

FIG. 1 describes the basic operations of a logic simulator

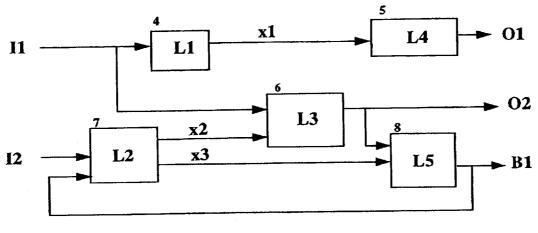

FIG. 2 depicts a circuit model used by a logic simulator to model a user design;

- FIG. 3 illustrates a flow chart that describes a detailed event-driven logic simulation process which is an expansion of Box 2 in FIG. 1 to show that the flow is independent of which HDL language is used;

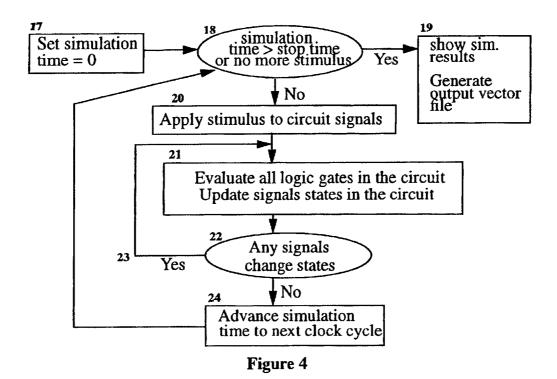

- FIG. 4 describes a detailed cycle-based logic simulation 5 flow as an expansion of Box 2 in FIG. 1 to show that the flow is independent of which HDL language is used;

- FIG. 5 shows a sample graphical waveform window used by either an event-driven or a cycle-based logic simulator to depict simulation results;

- FIG. 6 shows a sample state listing window used by either a event-driven or a cycle-based logic simulators to depict simulation results;

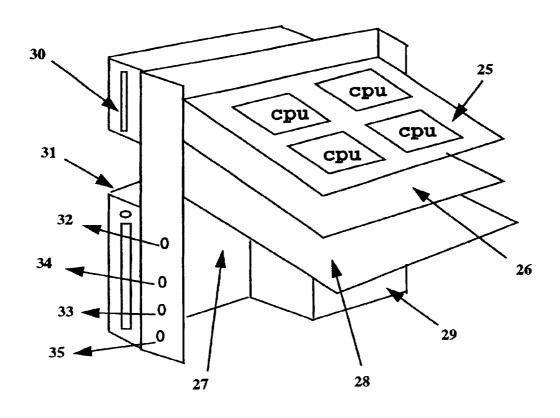

- FIG. 7 shows a typical configuration of various system components of a multiprocessor system that can run either 15 UNIX or Windows™ operating system;

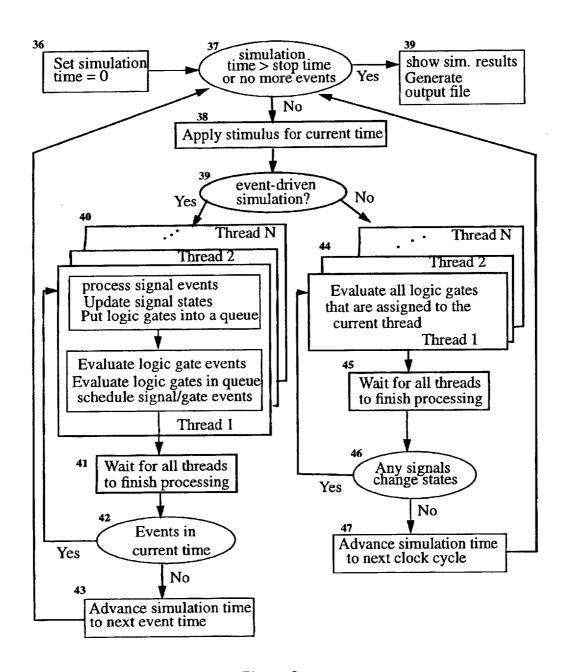

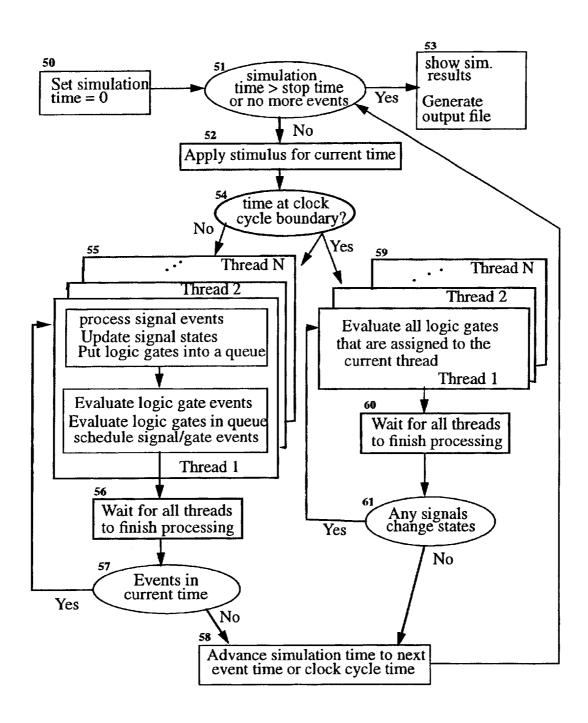

- FIG. 8 shows the logic simulation algorithms (eventdriven and cycle-based) modified for multiprocessor systems;

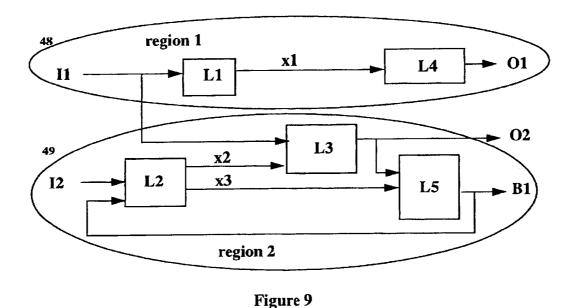

- FIG. 9 shows the partition of a circuit into different regions from which each of the regions is simulated by a separated thread in a cycle-based logic simulator;

- FIG. 10 shows a sample clock definition file for cycle-based logic simulation wherein users may optionally specify certain logic regions be processed using cycle-based, and the rest of the circuit will be processed using event-driven method;

- FIG. 11 shows the logic simulation algorithm for mixed event-driven and cycle-based simulation on a multiprocessor system;

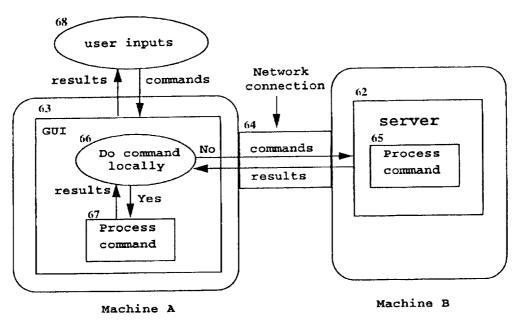

- FIG. 12 shows the use of a UI program to connect to a remote server (running on a different machine) via a local area or wide area network to pass user's commands server program;

- FIG. 13 shows a sample UI window for scheduling simulation job;

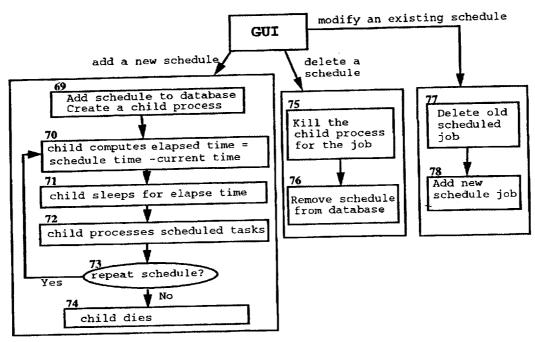

- FIG. 14 shows the process flow for handling of simulation job schedules;

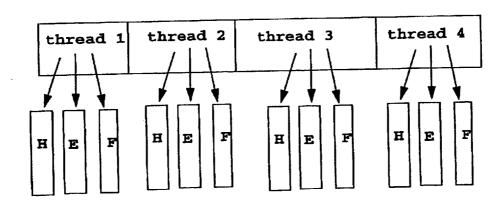

- FIG. 15 shows thread-specific private data to minimize thread manipulation overheads;

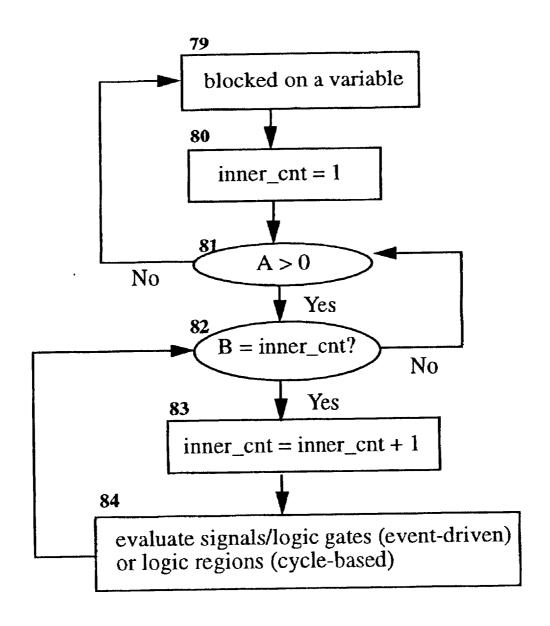

- FIG. 16 shows the process flow of a function to be executed by multiple threads concurrently in logic simulation wherein the threads are blocked by conditional variables:

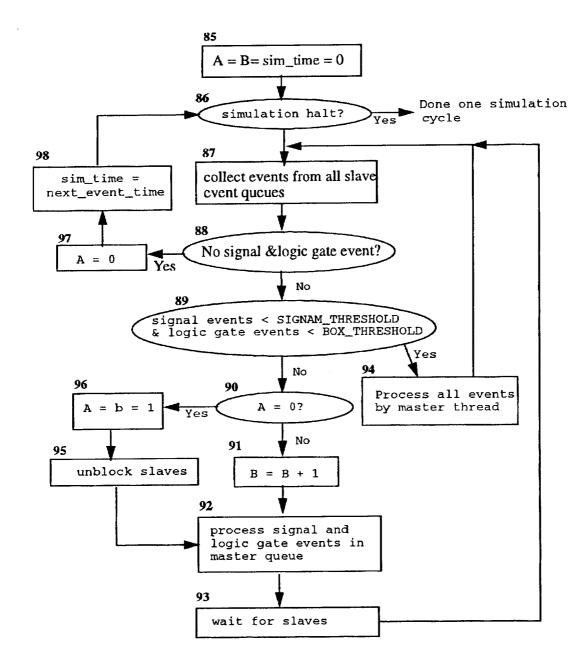

- FIG. 17 shows the process flow of an event-driven simulation algorithm as executed by a master thread;

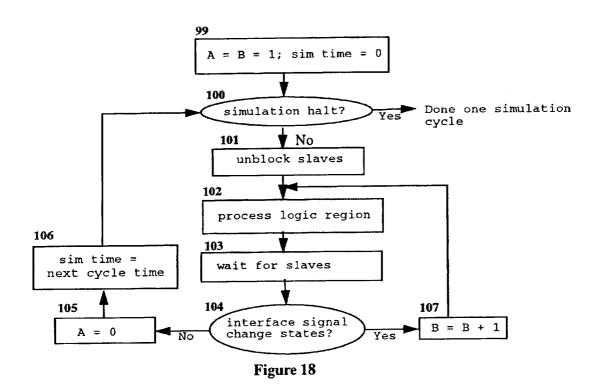

- FIG. 18 shows the process flow of a cycle-based simulation algorithm as executed by a master thread;

- FIG. 19 shows the pseudo code of a function to be executed by multiple threads concurrently in logic simulation using SWAP;

- FIG. 20 depicts the process flow of an event-driven and cycle-based simulation algorithm that is executed by all master and slave threads concurrently in each simulation iteration:

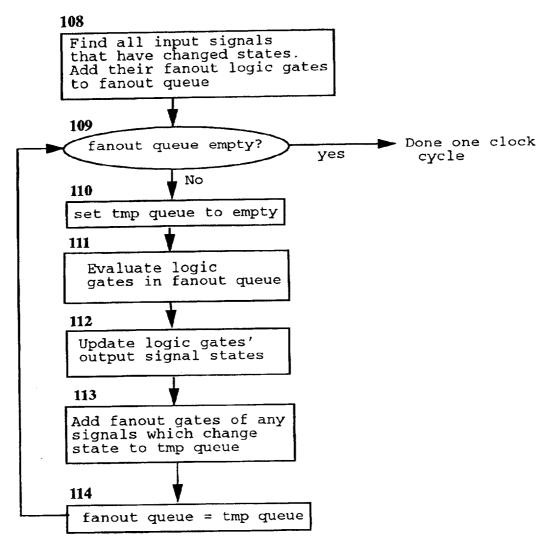

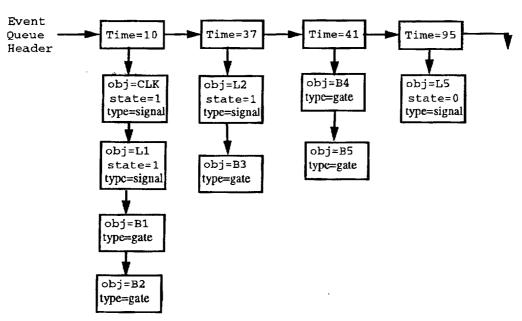

- FIG. 21 shows an example event queue for event-driven logic simulation;

- FIG. 22 shows a sample simulation vector file; and

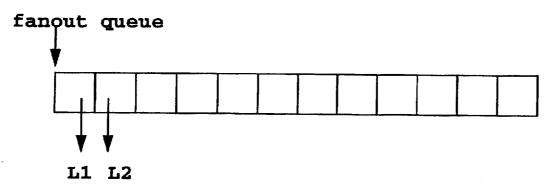

- FIG. 23 shows an example fanout queue for event-driven logic simulation wherein the fanout queue is a linear array 60 of pointers to logic gates to be evaluated;

## DESCRIPTION OF THE BACKGROUND TECHNOLOGY

#### Circuit Model for Logic Simulation

Referring to FIG. 2, there is shown a logic simulator that models a user design (i.e., a circuit) shown as a directed

6

graph consisting of a series of "logic gates" and signals. The signals namely, I1, I2, O1, O2, B1, x1, x2 and x3, in the directed graph are named in accordance to on-chip buses in VLSI designs. The signals carry discrete logic values and may be single-bit or multiple-bits. The Logic gates, designated as boxes L1 4, L2 5, L3 6, L4 7, and L5 8 in FIG. 2, may be of different types to represent different logic functions in the VLSI design. For example, the L1 4 logic gate may be an adder, and the L2 5 logic gate may be a 4-bit counter, etc. Specifically, each logic component (e.g., a counter, a clock generator, or a memory module) in the user design is mapped to one or more logic gates, which are interconnected by the correspondent signals to reflect the actual connectivity of the logic elements in the user design.

For simulation, user-defined input stimuli are usually applied to the primary signals and bi-directional signals (e.g., 11, 12, and B1) of a circuit. When a signal changes state, its fanout logic gates will be evaluated. This evaluation may cause the fanout signal(s) of the logic gate to either changes state immediately or be scheduled to change states at a future time. The logic simulator can keeps track of these events propagation by using the directed graph.

#### Logic Simulation Algorithms

The logic simulation algorithms described hereunder are applicable to both event-driven and cycle-based logic simulators as well as to the concurrent execution of these logic simulation algorithms on multiprocessor workstations as provided by the invention.

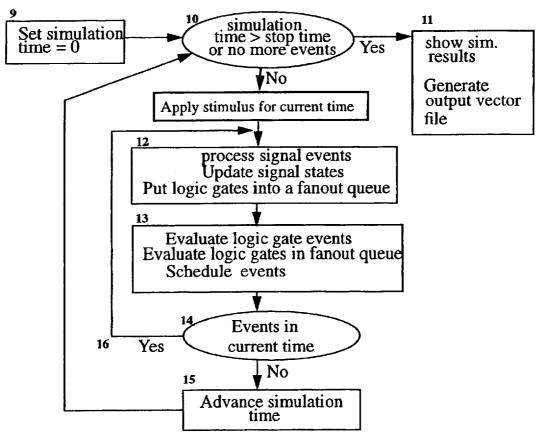

Referring to FIGS. 3 and 4, there depict detailed logic simulation processes respectively for the event-driven and cycle-based logic simulators. Prior to performing any step illustrated in this flow, a user HDL design (either coded in VHDL, Verilog, or a combination of both) should have been compiled into the simulator database. Moreover, user-defined input stimuli for the simulation run should have also been loaded into the simulator memory.

FIG. 3 illustrates the event-driven simulation process in which the input stimulus consists of new states to be assigned to the primary input and bi-directional signals (e.g., I1, I2, and B1 of FIGS. 2) of the design being simulated, at various simulation time points. The simulator schedules events for these selected signals to change states according to the stimulus specification. To manage these scheduled 45 events, the simulator chains all events that are to be processed at the same simulation time point into a linked-list. A linked-list may contain both signal events and logic gate events. There may be multiple linked-list maintained by the simulator during simulation, and it sorts and stores all these linked-lists in a linear event queues, in increasing scheduled times (FIG. 21 shows an example of an event queue). The simulator removes each of these linked-lists from the queue in a first-in-first-out manner. It also advances the simulation time according to the scheduled time specified in each linked-list so processed.

Referring to FIG. 3, the logic simulator begins simulation by setting the simulation time to 0 as indicated by a step 9. It then checks, as indicated by a step 10, if the current simulation time exceeds a user-specified maximum simulation run time, or if there is no event pending in the event queue. If all of the conditions indicated by the step 10 are true, the simulation is halt as indicated by a step 11, and the logic simulator will proceed to show the simulation results to users via a graphic waveform windows and/or a tabular state listing windows (see FIGS. 5 and 6). The simulator can also generate a hard copy vector file (see FIG. 22) to document the simulation results.

#### US 6,466,898 B1

7

If the simulation time is less than the user-defined limit, and there are certain event(s) pending, the simulation proceeds to a step 12 by checking the event queue for any signal events and/or logic gate events pending for the current time. If there are signal events, the logic simulator will process the signal events first, and then it will process any logic gate events afterward.

The signal events are processed, as indicated by the step 12, by updating the specified signals' states to their new values, and also put their fanout logic gates either into a fanout queue for evaluation or to schedule them to be evaluated at some future times (i.e., as new logic gate events). The fanout queue (see FIG. 23) is a linear array that holds pointers to logic gates that are to be evaluated in the current simulation time (after all signal events are processed). The logic gates in the fanout queue are tagged, so that if multiple inputs of a logic gate change state at the current simulation time, the logic gate is put into the fanout queue once only.

The logic gate events are processed next, as indicated by a step 13, which includes evaluating logic gates specified in these events, and schedule any fanout signals of these logic gates to change states in future simulation times. Furthermore, some logic gates may need to be re-scheduled for evaluation in future times (for example, the logic gate may be a clock generator which drives a clock signal to 25 change states in a fixed time interval) this will result in new logic gate events being put into the event queues.

After all logic gate events are processed, any logic gates stored in the fanout queue will be removed from the queue and be processed in the same manner as the aforementioned 30 logic gate events.

When all signals and logic gates are processed, the simulator will check the event queue to determine if there are still any (zero-delay) signal and/or logic gate events need to be processed as indicated by a step 14. If there are still such events remained to be processed, the simulation iteration repeats by going back to the processing of these events as indicated by a step 16 until these events are processed through the steps of 12, 13, and 14.

Referring back to the step 14, if there are no zero-delay 40 events remained to be processed for the current time, the simulator advances the simulation time to the next event-pending simulation time, as indicated by a step 15, which causes the simulation cycle to be repeated by reverting the process to the step 10 to check the simulation stop conditions

FIG. 4 illustrates the cycle-based simulation process in which the input stimuli consist of new states to be assigned to circuit signals at each clock cycle. The simulator does not schedule events for these stimuli; instead it reads and applies 50 the stimuli vectors sequentially at the start of each clock cycle.

For cycle-based simulation, the simulation process is similar as that described for event-based simulation above except that there is no event queue need to be processed. In every simulation cycle, the logic simulator begins simulation by setting the simulation time to 0 as indicated by a step 17, it then checks, as indicated by a step 18, if the current simulation time exceeds a user-specified maximum simulation run time, or if there is no more stimulus left. If any of the conditions indicated by the step 10 is true, the simulation is halt as indicated by a step 19, and the logic simulator will proceed to show the simulation results to users via a graphic waveform windows and/or a tabular state listing windows (see FIGS. 5 and 6). The simulator can also generate a hard copy vector file, which contains the simulation results (see FIG. 22).

8

If the simulation time is less than the user-defined limit, and there is stimulus vector pending, the simulation proceeds to a step 20 wherein the simulator will apply the input stimulus for the current clock cycle, and then evaluates all logic gates in the circuit design at repeated iterations, until no more signals change states as indicated in steps 21, 22 and 23. The simulator then advances the simulation time to the next clock period as indicated in a step 24, and repeats the simulation cycle by reverting the process to the step 18.

#### Multiprocessor System

FIG. 7 depicts a typical multiprocessor system. The multiprocessor system comprises one or more CPU boards 25. Each of the CPU board hosts two or more CPU chips, cooling fans, and second-level cache memory. The number of CPUs on any multiprocessor system should be in multiple of two (i.e., a system may have two CPUs, four CPUs, or eight CPUs, etc). All CPUs on a multiprocessor system are usually of the same brand/model and run at the same speed. Except for their dedicated second-level cache memory and cooling fans, all CPUs on a multiprocessor system share all other resources: main memory 26, system bus system 27, floppy, video, mouse and hard-disk controller, etc 28-35.

The multiprocessor system also contains other components that are the same as any single-processor system. These include a hard-disk drive 29, floppy disk drive 30, CDROM drive 31, and external device controllers such as keyboard 32, printer 33, mouse 34 and modem 35.

A multiprocessor system may run UNIX, Windows™, Linux, or any other operating systems that support symmetric multiprocessing (SMP). SMP means the operating system that can assign an equal amount of operating tasks to all CPUs on the system, so that the system can run multiple jobs concurrently.

When a non-multithreaded application is run on a multiprocessor/SMP system, it will be treated as one operating task by the operating system. It will not be executed concurrently on multiple CPUs and hence its performance will not be improved over that on a single-CPU system. A multithreaded application, on the other hand, can run its separate threads on multiple CPUs concurrently. Thus a multithreaded application's performance can be accelerated on a multiprocessor/SMP system. In a multithreaded application, there may be a thread that controls the execution of all other threads. The controlling thread is called the "master thread". The other threads that are controlled are known as the "slave threads". The "master thread" and "slave threads" are used herein to describe the methods for multithreaded logic simulation according to the invention and should have the above-defined meanings.

In the rest of this specification, the term "multiprocessor systems" represents any commercial multiprocessor/SMP systems.

## DETAILED DESCRIPTION OF THE INVENTION

1. Multithreaded HDL Simulator Uses Single Program for VHDL and Verilog Design Verification

This invention discloses a new logic simulator that supports both the VHDL and Verilog design languages for both event-driven and cycle-based simulation in a single program, and uses multithreaded methods to accelerate the simulator's performance on multiprocessor platforms. These features aid users to cut down the development time by not having to learn a new HDL language in order to use the simulator. In addition, it allows the users to mix-and-match

HDL design files from different design groups (in the company) or from vendors, and yet be able to accelerate their simulation on multiprocessing systems.

Table 2 lists the major commercial HDL simulators and their features as compared to the invention. Note that none of the prior art simulators has the ability to support both VHDL and Verilog languages in a single multithreaded application. Moreover, none of the prior art simulators is capable of providing an application that can run on the UNIX, Linux, and Windows™ platforms.

TABLE 2

| Comparison of the invention with major Commercial Logic Simulators |           |                |                                   |     |       |  |  |

|--------------------------------------------------------------------|-----------|----------------|-----------------------------------|-----|-------|--|--|

| Product                                                            | Vendor    | HDL language   | Platforms                         | мт  | Sim   |  |  |

| vcs                                                                | Synposys  | Verilog        | UNIX,<br>Windows                  | No  | Event |  |  |

| VSS                                                                | Synopsys  | VHDL           | UNIX,<br>Windows                  | No  | Event |  |  |

| Cyclon                                                             | Synopsys  | VHDL           | UNIX,<br>Windows                  | No  | Cycle |  |  |

| SpeedSim-MT                                                        | Synopsys  | VHDL           | UNIX                              | Yes | Event |  |  |

| LeapFrog                                                           | Cadence   | VHDL           | UNIX,<br>Windows                  | No  | Event |  |  |

| Verilog-XL,                                                        | Cadence   | Verilog        | UNIX                              | No  | Event |  |  |

| Polaris                                                            | Avanti    | Verilog        | UNIX                              | Yes | Cycle |  |  |

| SpeedWave                                                          | Quickturn | Verilog        | UNIX                              | Yes | Cycle |  |  |

| QuickHDL                                                           | Mentor    | VHDL & Verilog | UNIX,<br>Windows                  | No  | Event |  |  |

| Invention                                                          |           | VHDL & Verilog | UNIX,<br>Linux,<br>and<br>Windows | Yes | Both  |  |  |

Legend:

Event = Event-driven simulation.

Cycle = Cycle-based simulation

MT = multithreaded kernal.

Sim = simulation method

(A) Simulator Supports Both the VHDL and Verilog Languages in a Single Program

The logic simulator that supports both the VHDL and Verilog languages in a single program according to the 40 invention is discussed. Specifically, the logic simulator (event-driven and cycle-based) has separate compilers for the VHDL and Verilog source files. When the simulator compiles a user-specified HDL source file, it will pre-examine the file content to detect automatically the coded 45 file language. It will then invoke an appropriate compiler to process that file. Thus, unlike other prior art, the simulator provided by the invention does not require a special program invocation switch, nor does it require feature makes the simulator easy for user to use, and is less error pro n e for 50 operation.

Since the VHDL language is case-insensitive, whereas the Verilog language is case-sensitive, when users compile multiple design files coded in a combination of both of these two languages, they need to specify a program invocation switch to instruct the simulator that either the Verilog compiler should convert all design object names into the same case as that used by the VHDL compiler, or that the VHDL compiler should preserve object names. This is needed so that the simulator can resolve signals or logic gate names that are referenced in a VHDL source file but defined in a Verilog file, or vice versa. This program switch is, however, not needed if users are compiling either VHDL-only or Verilog-only source files.

Since VHDL supports a smaller set of logic states than 65 verilog, for mixed-language designs the simulator will automatically map VHDL signal states to Verilog signal states.

10

This approach has been found adequate for most ASIC (Application Specific Integrated Circuit) and FPGA (Field Programmable Gate Array) designs. However, if users need more control on the logic states mapping between the two languages, they can specify a configuration file which describes such mapping, and instruct the simulator to read that configuration file, before it compiles any HDL design files. Specifically, in the configuration file, users will specify how each IEEE std. 1164 MVL9 (multi-value logic level) state (for VHDL) is mapped to which signal state(s) in Verilog. Furthermore, if users define their own data types in their VHDL design files, they can specify in the configuration file how to map those user-defined states to Verilog signal states.

When compiling user's HDL design files, any signal in the design that connects a VHDL logic gate and a Verilog logic gate will be modified by the compiler to pass through a state conversion "logic gate". During simulation, this logic gate will perform state conversion function between VHDL states and Verilog states according to either the simulator's default mapping or user-defined mapping.

To accomplish the aforementioned purposes the simulator compiles VHDL and/or Verilog design files into a common database to which the event-driven and cycle-based logic simulation will be performed. After a design is compiled, users may instruct the simulator to compile the IEEE-defined SDF (Standard Delay File) files to back-annotate post-physical layout delay timing data to the design in the database. Like compiling mixed language design files, users may use the same program invocation switch to instruct the invention SDF compiler to either preserve the letter cases in the SDF file (if the database was compiled to be case sensitive), or to ignore cases in the SDF file (if the database was compiled to be case insensitive).

35 (B) Multithreaded Simulation For VHDL and Verilog Designs

Once users' VHDL and/or Verilog designs have been compiled into the simulation database, they are being processed by the same multithreaded simulation engine. Thus, the simulation of VHDL-only, Verilog-only, and mixed VHDL and verilog designs are accelerated in the same manner.

(C) Special Logic Simulation Algorithms on Multiprocessor Systems

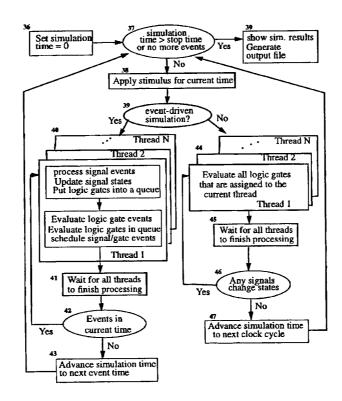

Referring to FIG. 8, there is shown a new logic simulation process flow for event-driven and cycle-based simulation on multiprocessor systems according to the invention. The objective of this new logic simulation algorithms is to accelerate the simulation process to reduce product development time and costs for users.

As stated above, the basic logic simulation algorithms on a multiprocessor system are similar to that on a single-CPU system for event-driven and cycle-based logic simulation, as shown in FIGS. 3 and 4 (i.e., as compared to those steps shown in 36, 37, 38 and 39, in FIG. 8), except the processing of signals and logic gates on a multiprocessor system are modified. The objectives of these modifications are to maximize concurrency and minimize thread synchronization overhead in the simulation process. These modifications and their benefits are described in more detail later.

(i) The modification to Event-Driven Logic Simulation

Referring to FIG. 8, the event-driven logic simulation on a multiprocessor system according to the invention is modified to process multiple signals concurrently rather than serially by multiple threads as shown in a step 40, which run concurrently on multiple CPUs. Specifically, a thread in parallel with the others can do the updating of an individual

signal state. Then, each signal's fanout logic gates are pushed into a per-thread specific fanout queue (steps 40 and 41). These fanout logic gates and any logic gate events for the current simulation cycle will be evaluated by each thread concurrently. Once all threads have completed processing their assigned signals and logic gates events, a master thread will check if there are further (zero-delay) events to be processed in the current simulation cycle (step 42). If there are, the simulation iteration repeats the steps 40–42, or the master thread advances the simulation time to the next 10 event/clock cycle time (step 43), and starts a new simulation cycle (step 37).

cycle (step 37).

When logic gates are processed concurrently by multiple threads, any new signal or logic gate events that are generated from these evaluation are scheduled in a per-thread 15 specific event queue, and the event records are allocated from the per-thread specific heap memory region. In this way, there is no thread synchronization overhead in scheduling events for future simulation time points.

(ii) The Modification to Cycle-Based Simulation

Referring jointly to FIGS. 8 and 9, the cycle-based logic simulation on a multiprocessor system according to the invention is modified to process multiple signals concurrently rather than serially by multiple threads.

As illustrated in FIG. 9, the simulator will partition the 25 circuit being simulated into different regions (48 and 49). Each region will consist of signals (ie., I1, x1 and O1 in region 48 and I2, x2, x3, O2 and B1 for region 49) and logic gates (i.e., L1 and L4 in region 48 and L2, L3 and L5 in region 49), and is assigned to be processed by a dedicated 30 thread. Thus, during simulation, all threads are processing different regions of the circuit, and there are minimum interactions among threads. However, since interface signals between regions may change states after the regions have been evaluated. Thus there is a need for cycle-based simulator to repeatedly evaluating logic gates in all regions within any simulation cycle, whenever there are inter-region signals that change states.

Specifically referring back to FIG. 8, at the start of each clock cycle, the master thread will wake up all slave threads to begin evaluating all logic gates in their dedicated logic regions (step 44). Logic gates in each regions are ranked, such that all logic gates near the inputs of a region are evaluated first (e.g., L1 in region 48, and L2 in region 49, of FIG. 9), then their fanout logic gates are evaluated next (i.e., 45 L4 in region 48, and L3 and L5 in region 49, of FIG. 9), and the process continues for subsequent logic levels, until all logic gates in the regions are evaluated. This method ensure most input signals of a logic gate are updated, before the logic gate is being evaluated.

When a logic gate is evaluated, if any of its output signals change states, the change will occur immediately because cycle-based simulation does not model propagation delays in circuits. When all threads are done processing their logic regions, the master thread will check if any interface signals between regions have changed states (step 46 of FIG. 8). If there are, the master thread will instruct all the slave threads to repeat the evaluation of their regions (steps 44–45). Otherwise, it will advance the simulation time to the next clock cycle time, and starts a new simulation cycle (steps 47 on one unit

(iii) To Support Both Event-Driven and Cycle-Based Logic Simulation in a Single Program

The compilations of HDL design files are the same for both event-driven and cycle-based simulation. The simulator 65 also uses the same design database for both event-driven and cycle-based simulation. However, prior to running cycle-

12

based simulation, users must specify to the simulator the clock signal(s) that are to be used to define the clock cycle periods for the simulation run. Users can specify these clock signal names (and optionally their clock cycle periods, if they are to be different from those described in the HDL files) in a text file and specify that file's path name to the simulator, via a program switch, when invoking the simulator. During simulation, at each simulation cycle the tool will check if there are clock signals defined and it will perform cycle-based simulation accordingly (steps 44-47 of FIG. 8) or otherwise, it will perform event-driven simulation (steps 40-43 of FIG. 8).

As illustrated in FIG. 10, there is shown a sample clock definition file for cycle-based logic simulation. Users may optionally define the "Cycle=" statements in this file to specify logic regions which are to be processed using cycle-based, and the rest of the circuit will be processed using event-driven method. For example, the statement "Cycle=(CLK, L1, L2)" means all logic regions driven by the CLK signal, and those that contain the L1 and L2 logic gates will be processed using cycle-based method. While other logic regions will be processed using event-driven method.

Accordingly, it is now possible to perform mixed event-driven and cycle-based simulation on a circuit according to the invention. Users can specify to the simulator (via the clock definition file) that some logic components in their circuits are to be evaluated using event-driven method, while other components in their circuits are to be evaluated using cycle-based manner. In this situation, the compiler will partition the circuits into event-driven logic regions and cycle-based logic regions. Then during simulation, each thread will examine their assigned region type, and performs either event-driven or cycle-based simulation on their regions, accordingly.

FIG. 11 shows the modified simulation process flow for the mixed event-driven and cycle-based simulation on a multiprocessor system. The simulation process is similar to that described in FIG. 8 except for certain modifications. Note that cycle-based logic regions are evaluated at userspecified clock cycle boundaries only (step 54), whereas event-driven logic regions may be executed more often than their cycle-based counterparts. Thus at the beginning of each simulation cycle (step 54 of FIG. 11), the master thread will check if the current time is at the beginning of a clock-cycle boundary. If it is not, it will invoke threads to evaluate event-driven regions only (steps 55-57 of FIG. 11). Otherwise, it will invoke threads to process both eventdriven and cycle-based regions. Threads for cycle-based regions will evaluate logic gates in their assigned regions (steps 59-60 of FIG. 11), whereas threads for event-driven regions will do work only if there are events in their event queue for this clock cycle time (steps 55-57). In addition to the above, at the end of each simulation cycle (step 58 of FIG. 11), the master thread will advance the simulation time to either the next event time or clock cycle time, whichever comes sooner.

2. Multithreaded HDL Simulator Supports Scamless Access of Network Resource for HDL Design Compilation and Simulation

One unique feature provided by the invention is to use a distributed client/server architecture to allow users to compile and simulate their HDL designs on either local or remote machines on the Internet or intranets such that the users can perform remote logic simulation without the need of any internetwork tools like telnet, or rexec programs. The local and remote machines suitably employable may be

UNIX, Linux, or Windows™-based machines or other platforms. The advantages of this feature is to allow users to maximize the use of their hardware resources and to receive the return on investment of their hardware and software system, to improve engineering productivity to cut down 5 time and costs.

Referring to FIG. 12, to support remote compilation and simulation, the users need to install a server or a server program 62 provided by the invention on the respective machines networked with the Internet or Intranets. Once the 10 server program 62 is installed, the users then run a UI (user interface) program 63 on their local hosts. This UI program 63 allows the users to specify a remote machine name, and a remote directory pathname, on which they desire their HDL design compilation and/or simulation to be performed. 15 If the users do not specify these parameters, then they are default to the local machine and to the current work directories of the users. As such, for local processing, users' HDL design compilation and/or simulation will be processed and displayed locally in accordance with steps 66 and 67. If a 20 design is compiled and/or simulated on a remote hosts, the UI program 63 will open a network connection 64 to the server process on each user-specified host, and then transmits the user's commands to the server to be executed at the user-specified directory 65. After the commands are 25 executed, any console output and/or simulation results are automatically transferred back to the users' UI program 63 for display. In addition to all that, the users can also use the UI program 63 to browse any compiled design databases that are resided on local or remote machines.

The remote simulation capability allows users to treat any network machines in the same manner as their local machines. Thus, the users can readily share and use design data that are scattered on the Internet or intranets to save times and improve productivity by eliminating the need for manually copying files across machines or the need for physically logging-on to remote machines to run simulation.

To use the network-based computing feature, the users only need to install and run the server program 62 on any remote hosts to which they are connected or to which they wish to have access. Server hosts and users local hosts can be of different platforms, and may be connected via the Internet or Intranets.

The UI program 63 and the server program 62 according to the invention may communicate using any network transports and operating system supported interface functions. The latter includes using the Sun Microsystems Inc. Java<sup>TM</sup> Remote Method Invocation (RMI), sockets, Corba, DCOM, remote procedure calls, or any other methods.

For example, the server program 62 registers a set of 50 functions that can be called by the UI program 63 via the RMI. These functions include (1) compiling a HDL design file in a specified directory; (2) simulating a design residing in a specified directory; (3) displaying a database content in a specified directory; (4) showing the server version number, 55 and local host information; and (5) transferring a file to/from the UI. Furthermore, the server program registers its name with the RMI naming service program on its local host so that the server can run continuously on a remote host listening for the UI service requests.

On the user host (the client side), when a user specifies a remote host name and a remote directory pathname (in the UI menu) for compilation or simulation (step 68 of FIG. 12), the UI 63 will contact the remote host RMI naming service to obtain a handle for the server by specifying the registered 65 name of the server. If the UI obtains the handle successfully, it will use it to call the server's remote functions. However,

14

if the UI 63 cannot get the handle for a remote server, it will report to the user that an attempt to connect to a server on the specified host failed.

The server 62 provides a few functions that can be invoked by the UI 63 to transfer large files over the network. Specifically, any simulation results are stored in a file and are transferred from the server host to a UI host for display to the user. Furthermore, if a user wishes to compile a design on a remote host, but the design file is not on that remote host, the UI program 63 will instruct the server 62 to first obtain the design file before compilation.

Specifically, if a user is running a UI on host X, and he wishes a server on host Y to compile a design file that is on host X, the UI will first call the server on host Y to receive the design file and store it into a temporary file, then the UI will call the server a second time to compile the temporary file on the server host. The server will delete the temporary file once it completes its compilation. This is to avoid duplication of design files on network machines and causes confusion to users of which copy of the design file is the

As another example, if a user on host X instruct the UI to invoke a server on host Y to compile a design file that is resided on host Z, the UI will first contact the server on host Z to transfer the design file into a temporary file on host X, then it will call the server on host Y to receive the design file, and then compile it. This process could be modified such that the UI can instruct the server on host Y to copy the design file directly from the server on host Z, and then compile the file. This will save time and avoid creating a temporary file on host X. However, the user may (and often does) wish to view/edit the compiled design file on host X, thus it makes sense for the UI to make a local copy of the design file on host X. Furthermore, the current method also eliminates the need for the servers to communicate with each other, and thus reduces the invention code complexity.

In addition to providing compilation and simulation functions, the server according to the invention also provides some RMI functions that return the server version number and the server host name and workload information. This can be used by the UI to inform users of the status of remote server hosts. The users can use the information to select the latest version of remote servers and/or those running on hosts with the lightest workload.

No prior art provides the similar remote simulation capability as aforementioned. Furthermore, no prior art has used the Sun Microsystems Inc. Java<sup>TM</sup> RMI method for any network-based logic simulation.

3. Multithreaded HDL Simulator Provides and Supports Simulation Job Scheduling

Referring now to FIG. 13, the UI according to the invention further provides a sophisticated menu for users to define, query, modify, or delete simulation jobs. Specifically, a user may define one or more jobs, such that each job instructs the UI to launch HDL compilation and/or simulation of designs on a local or a remote machine, at the user-specified time(s). Furthermore, the users may instruct the UI to repeat the job on a regular time interval (e.g., weekly, or daily). This benefits users by improving engione ering productivity and cut down development time and costs.

In addition to the above, a user may also instruct the UI to log events, send emails on the status of a job to a list of users, and/or to execute other shell commands (system commands or shell scripts) at the completion of a scheduled job. Consequently, this job-scheduling feature is very useful for large design teams to carry out regression testing of their

new releases at regular period. Moreover, it allows designers to balance the use of their network machines by scheduling simulation to run at non-overlapping hours on each machine

Under the current industry practice, for comparison purposes, users that use UNIX or Linux machines may write 5 their own cron jobs to schedule simulation events. This method requires the users to code and debug their cron files, which is timing consuming and error-prone. In addition, the cron job scheduling is not supported by the Windows<sup>TM</sup> platform. Using the simulator provided by the invention, 10 however, the users will find that it is much more efficient and less error prone to define simulation jobs. Furthermore, this feature is available across the UNIX, Linux, Windows<sup>TM</sup> (95/98/NT) or other platforms.

Referring to FIG. 14, to implement the job scheduling functions, the UI compiles all user-defined jobs into a binary "job description" file. This file is stored in a private directory. For each user-defined job, the UI will create a child process to handle that job. For each newly added user-defined job, the UI will create a child process to handle that job (step 69 of FIG. 14). The child process will run independently from the UI, and it will terminate when the target job has been completed.

Specifically, when the child process starts up, it will record its process identification number to a job entry in the 25 "job description" file. It then computes elapsed time, which is the difference between the schedule time and current time 70, and goes into a "sleep" mode 71 and wakes up only at the user-specified schedule time. For example, if a user defines a job at 10 pm, and specifies that the job is to be 30 executed at 12 am of the next day, the child process will sleep for 2 hours and then wake up to process the job. When the child process wakes up, it executes the job in accordance with the user specification 72. If the job is to compile/ simulate a design on a remote host, the child process will 35 contact a remote server to perform such functions, in the same manner as the UI does. After the job is completed, the child process will record in the job entry of the "job description" file that the job has been executed, and it will perform any post-processing operations (e.g., sends emails 40 to users, executes user-defined shell commands, and/or logs the job execution event to a file). After that, if there are still other schedule time(s) for the job, the child process will go back to sleep 73. Otherwise, it will terminate itself 74.

It should be noted that the use of the aforementioned 45 as: method instead of creating cron jobs for job scheduling has provided many advantages over the prior art. One notable advantage is that the method eliminates the need for cron supports and therefore makes job schedule applicable to the Windows™ platform, which generally does not support cron jobs. Furthermore, this method provides a preferred alternative for users to schedule simulation jobs on UNIX and Linux systems previously relying on the cron files because corn files are used system-wide on those systems by all users including those performing functions unrelated to job schedule, thus it may be undesirable to modify the cron files as it may adversely affect the abilities of the UNIX and Linux systems to perform other functions.

In the event that a host is rebooted and the invocation server is restarted, it will automatically read the "job description" file. If there are jobs yet to be executed but their correspondent child processes are no longer running, the server will create new child processes to handle these jobs. In this way, the job scheduling will remain intact despite that the system has been rebooted.

The job scheduling functions provided by the invention also allow a user to cancel a scheduled job via the UI. 16

Specifically, a user can identify a schedulad job by name, and instructs the UI to delete the job. The UI will first find the child process that is associated with the job and kills the child process 75. The UI then removes the corresponding job description file in its private database 76.

The job scheduling functions provided by the invention also allow a user to modify a scheduled job (e.g. change the HDL files to be compiled, or the simulation run options) via the function of UI program. Specifically, he will first instruct the UI to bring up the menu for the scheduled job (see FIG. 13), edits the menu, and then clicks the "OK" button. Once the menu is closed, the UI will first delete the existing scheduled job 77 and add new scheduled job 78 followed by creating a child process to reschedule the job (steps 69–74 of FIG. 14).

No prior art offer any job scheduling capability.

4. Advanced Concurrent Algorithms to Ensure Superior Scalability of Simulation Performance on Multiprocessor Computer Systems

Beside modifying the basic logic simulation (event-driven and cycle-based) for multiprocessor systems, special features are provided to further accelerate the simulation process on multiple CPUs concurrently so that the simulator according to the invention can consistently out-perform other simulators for event-driven and cycle-based simulation. Specifically, when a user runs a multithreaded tool on a n CPU system (where n>1), he would expect that the performance of the tool should improve by C \* n times, where C is an empirical constant as follows:

0.5>-C<-1

For example, if C is 0.75, then the expected speedup of a multithreaded tool on different configurations of a multiprocessor system are:

| - | Number of CPU | Speedup   |  |

|---|---------------|-----------|--|

|   | 2             | 1.5 times |  |

| ) | 4             | 3.0 times |  |

|   | 8             | 6.0 times |  |

Where the speed up of a multithreaded tool is computed as:

Speedup (x)=Performance on a multi-CPU system/Performance on a single-CPU system

If the C factor of a multithreaded tool remains at 1.0 on different number of CPU configurations, the tool is said to demonstrate a linear scalability. If the C factor of the tool is less than 1.0, then it is said to demonstrate a sub-linear scalability. Finally, if the C factor of the tool is above 1.0, then it is said to demonstrate a super-linear scalability. It is generally possible for a multithreaded tool to demonstrate sub-linear scalability on some test cases, and linear or even super-linear scalability on other test cases. If a tool consistently demonstrates linear to super-linear scalability on most test cases it processes, then it can be classified as a linear/super-linear scalable tool. Otherwise it is classified as a sub-linear scalable tool.

Table 3 below depicts the scalability benchmark results of the simulator provided by the invention as performed on a Sun UltraSparc™ (250 Mhz, 10-CPU, Solaris 2.6) platform 65 (i.e., the size is measured in number of logic gates in a test circuit; the times are measured in CPU seconds; and K=1024).It becomes apparent from these results that the

#### US 6,466,898 B1

17 simulator according to the invention will be classified as a linear/super-linear HDL simulator.

TABLE 3

| The scalability Benchmark Results of the multiprocessor systems provided by the invention |       |            |                      |                      |                             |  |  |  |

|-------------------------------------------------------------------------------------------|-------|------------|----------------------|----------------------|-----------------------------|--|--|--|

| Ckt:                                                                                      | size  | 1-CPU      | 2-CPU                | 4-CPU                | 8-CPU                       |  |  |  |

| test1                                                                                     | 100 K | 48.32 sec  | 20.83 sec<br>(2.3x)  | 10.53 sec<br>(4.6x)  | 4.97 sec<br>(9.7x)          |  |  |  |

| test2                                                                                     | 250 K | 374.49 sec | 164.67 sec<br>(2.3π) | 110.98 sec<br>(3.4x) | 59.77 sec<br>(6.3x)         |  |  |  |

| test3                                                                                     | 50 K  | 32.45 sec  | 17.49 sec<br>(1.9x)  | 10.32 sec<br>(3.2x)  | 5.23 sec<br>(6.2x)          |  |  |  |

| test4                                                                                     | 20 K  | 18.57 sec  | 9.72 sec<br>(1.9x)   | 6.07 sec<br>(3.1x)   | 3.31 sec<br>(5.6 <b>x</b> ) |  |  |  |

The simulator achieves linear and super-linear scalability by using special new concurrent methods that are described in the following sections. These methods are designed to maximize concurrency in the HDL simulation process, and to minimize the overhead in manipulation of multiple threads running on multiple CPUs concurrently. This renders superior and scalable HDL simulation performance. Furthermore, the methods are applicable for both event-driven and cycle-based logic simulations. The new concurrent methods used by the invention have not been described or implemented in any prior art.

(A) Methods to Minimize Threads Manipulation OverHead

Thread manipulation overheads include the time spent in

creation and destruction of threads, to schedule threads to

bind to hardware CPUs for execution, and to wait for threads

to complete their execution by other threads. Finally, if some

global data that may be concurrently accessed by multiple

threads, then those threads must be synchronized so that

none of the threads can modify those data if any one of most

of the other threads are currently reading or modifying those

data. Synchronization of the threads increases the simulation

time.