Case 8:13-cv-00546-JVS-AN Document 1 Filed 04/05/13 Page 1 of 260 Page ID #:4

FILED

Plaintiff Sony Corporation ("Sony") files this Complaint against Red.com,

Inc. dba Red Digital Cinema ("Red") pursuant to the patent laws of the United

States, 35 U.S.C. §§ 1 *et seq*, and alleges as follows:

## THE PARTIES

Sony is a corporation organized and existing under the laws of Japan

with offices at 1-7-1 Konan, Minato-ku, Tokyo, 108-0075, Japan.

7 2. On information and belief, Red is a corporation organized and existing 8 under the laws of Washington, having its principal place of business at 34 Parker, Irvine, California 92618, and doing business within this judicial district. Upon 9 10 information and belief, Red makes, imports into the United States, offers for sale, sells, and/or uses in the United States digital cinematography products, including, 11 12 without limitation, the RED ONE, EPIC, and SCARLET cameras; various Digital 13 Still & Motion Camera ("DSMC") modules such as the SSD MODULE, the DSMC SIDE HANDLE, and the REDMOTE; and various displays such as the RED 14 15 TOUCH 5.0" LCD and the RED TOUCH 9.0" LCD.

16

4

## JURISDICTION AND VENUE

This lawsuit is an action for patent infringement arising under the

patent laws of the United States, 35 U.S.C. §§ 1 *et seq*. This Court has subject

matter jurisdiction over this action pursuant to 28 U.S.C. §§ 1331 and 1338.

20 4. Red is subject to personal jurisdiction in this Court because, on 21 information and belief, it does and has done substantial business in this judicial District, including: (i) designating an agent for service of process in the State of 22 23 California; (ii) committing acts of patent infringement in this District and elsewhere in California and the United States; and (iii) regularly doing business or soliciting 24 25 business, engaging in other persistent courses of conduct, and/or deriving substantial revenue from products and/or services provided to individuals in this 26 27 District and in this State. On information and belief, Red's place of business in Irvine includes manufacturing, repair, data recovery, technical support, direct sales, 28

and product demonstration facilities. Further, on information and belief, Red has an

additional place of business at 846 North Cahuenga Boulevard, Los Angeles,

California 90038. On information and belief, Red's place of business in Los

Angeles includes a retail store as well as repair, data recovery, technical support,

product demonstration, and studio services facilities.

5. Venue is proper in this judicial district pursuant to 28 U.S.C. §§ 1391

and 1400(b) because Red regularly conducts business in this judicial district, has a

regular and established place of business in this judicial district, and/or because

certain of the acts complained of herein occurred in this judicial district.

10

## THE PATENTS-IN-SUIT

6. On August 15, 1995, the United States Patent and Trademark Office

("USPTO") issued U.S. Patent No. 5,442,718 ("the '718 patent"), entitled

"Apparatus and Method for Storing and Reproducing Digital Image Data Yielding

High Resolution and High Quality Video Image Data," naming Hideki Kobayashi

and Yasuo Ido as inventors. A true and correct copy of the '718 patent is attached

hereto as Exhibit A.

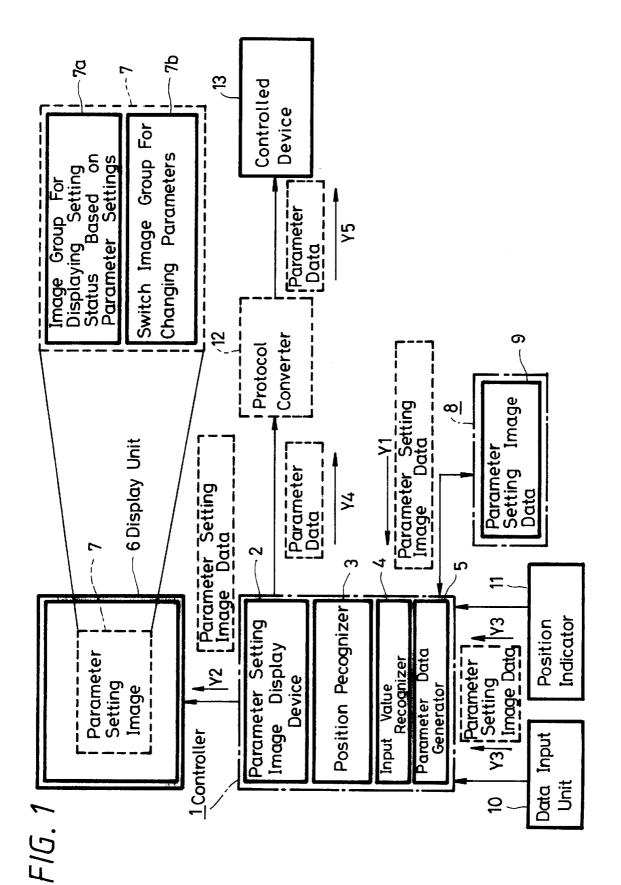

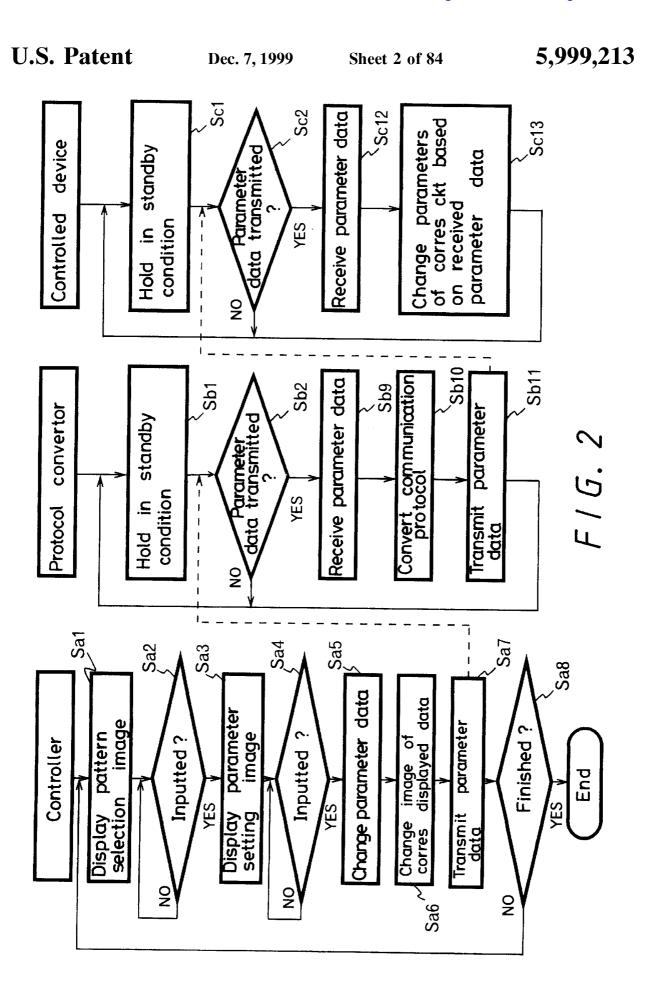

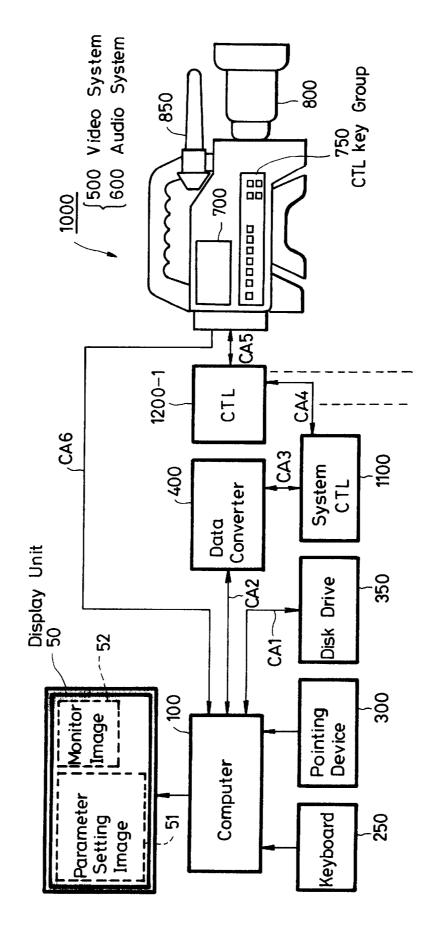

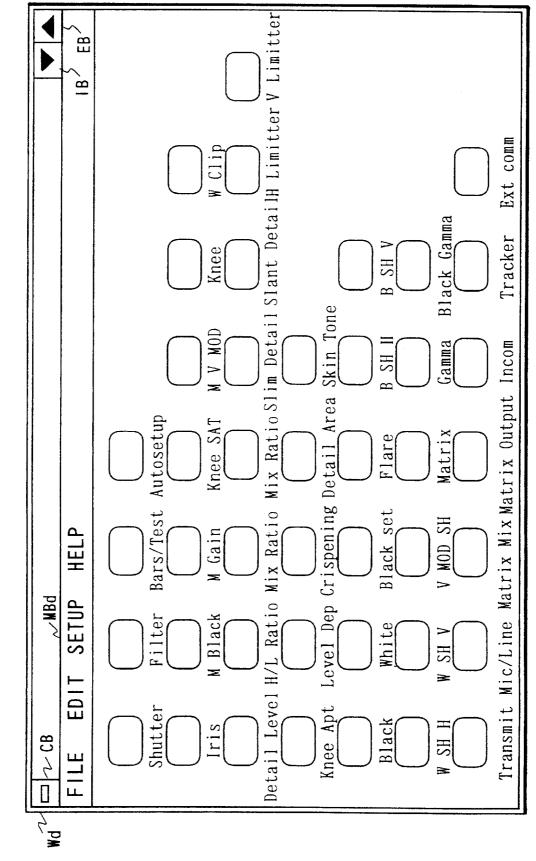

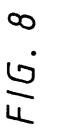

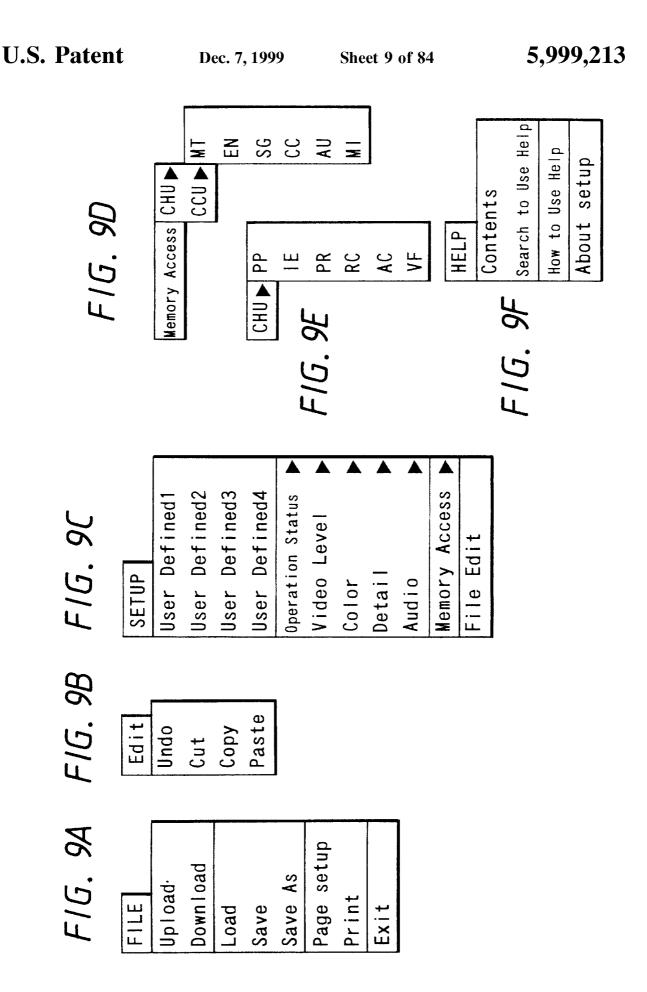

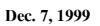

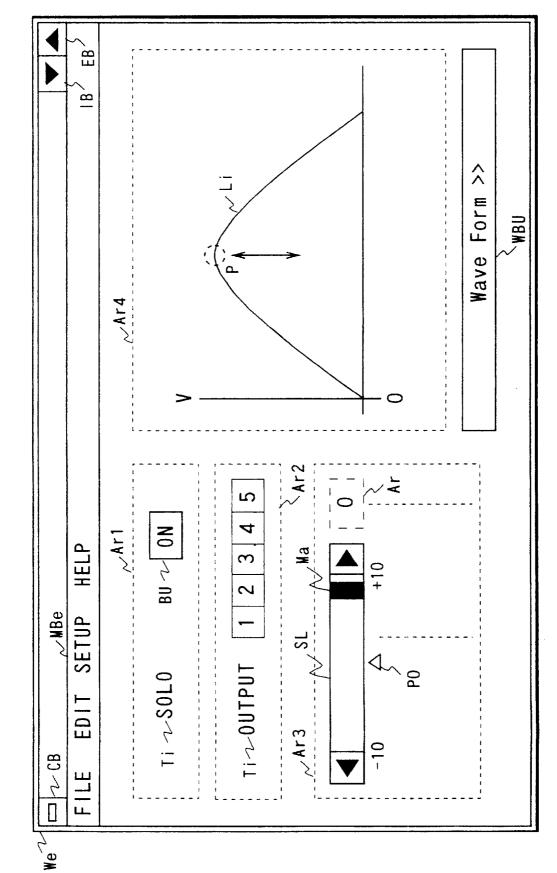

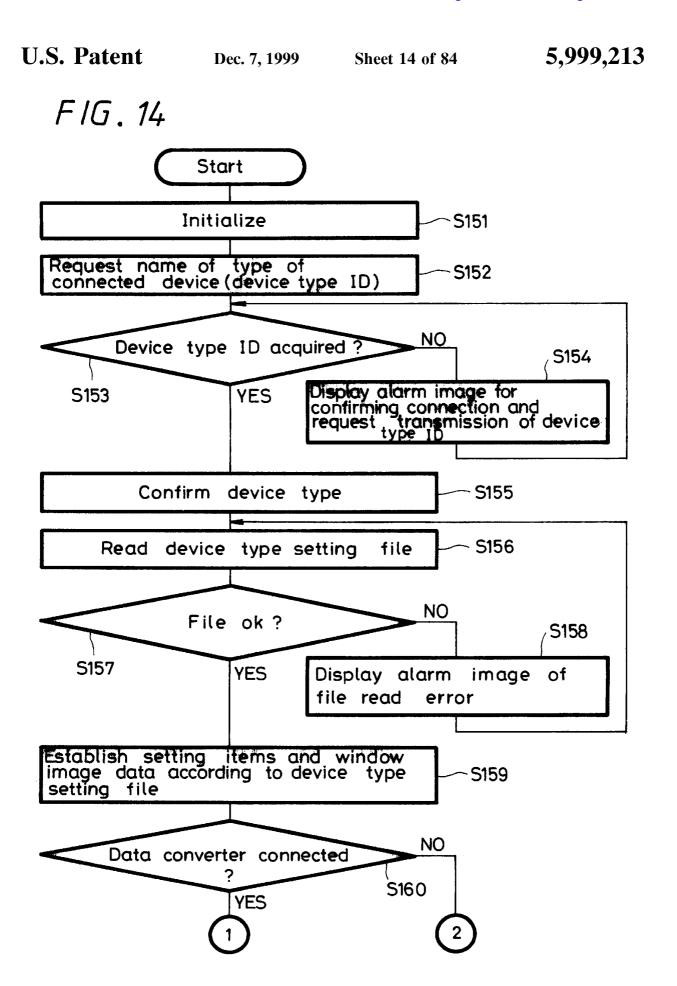

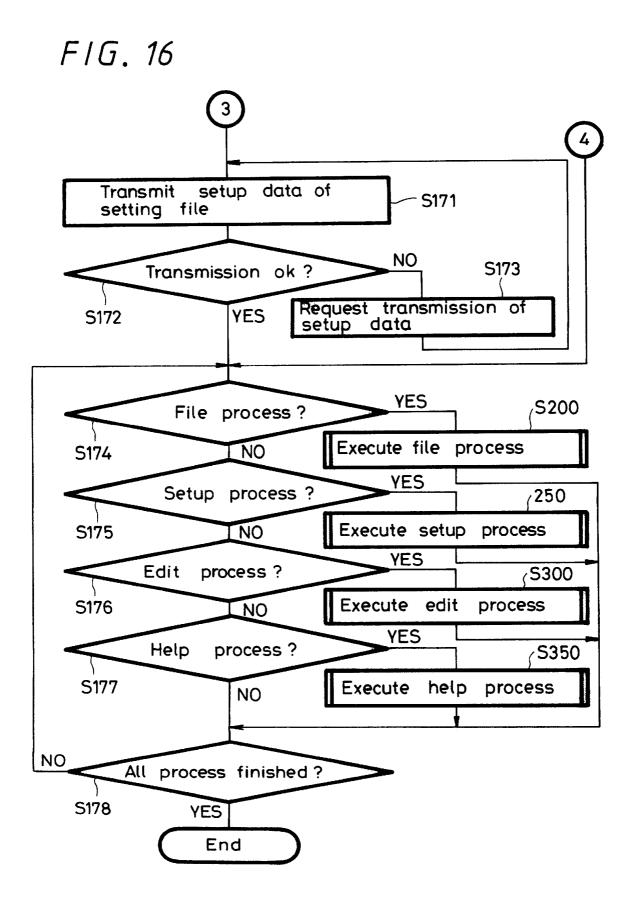

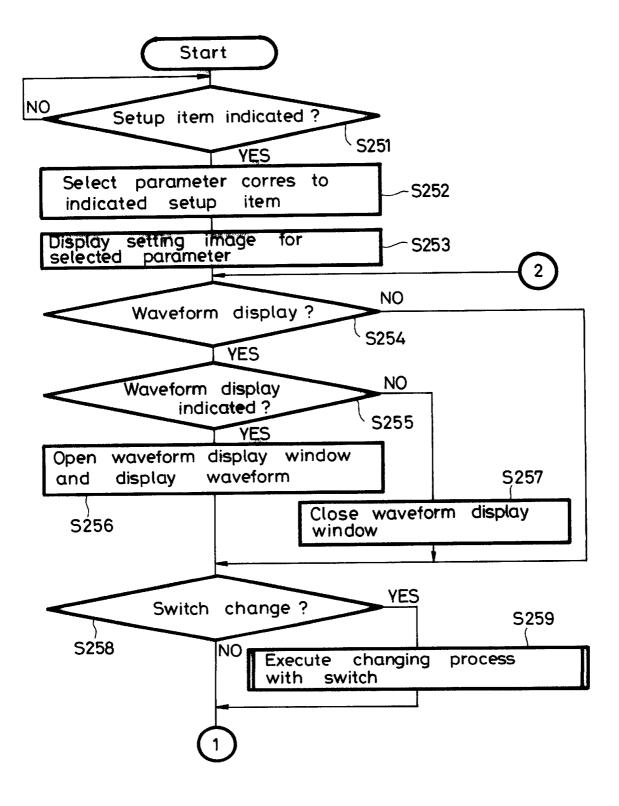

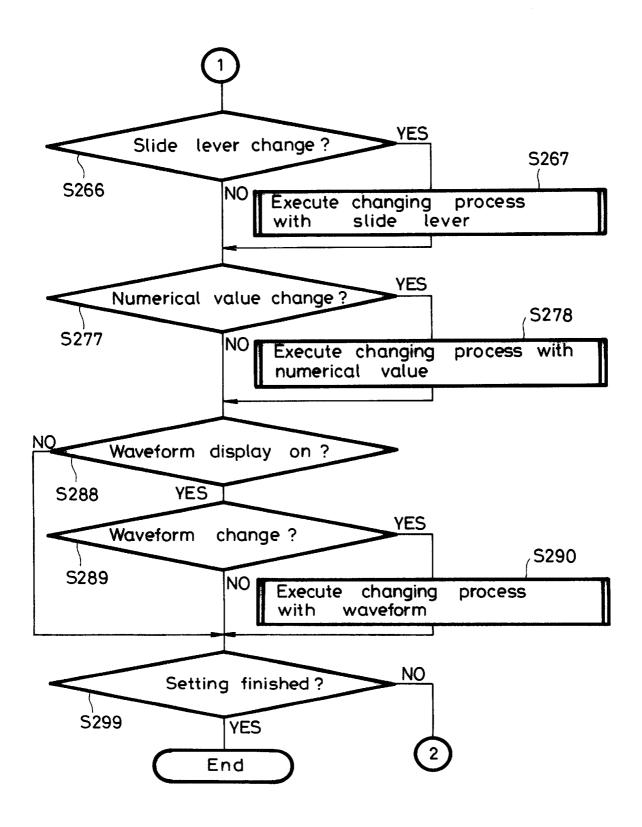

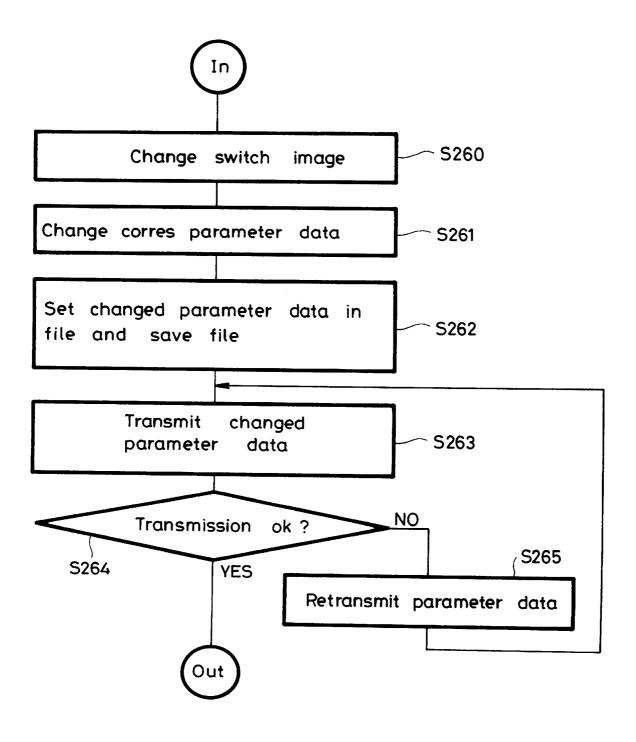

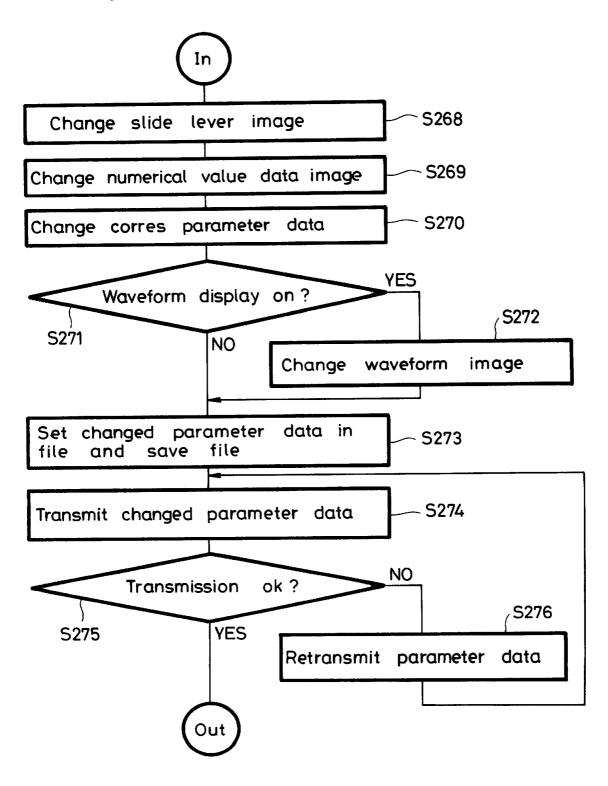

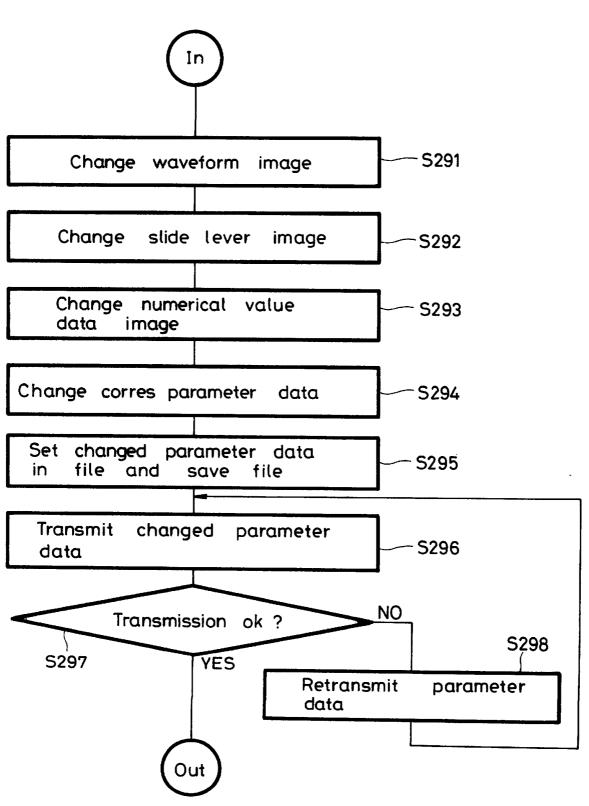

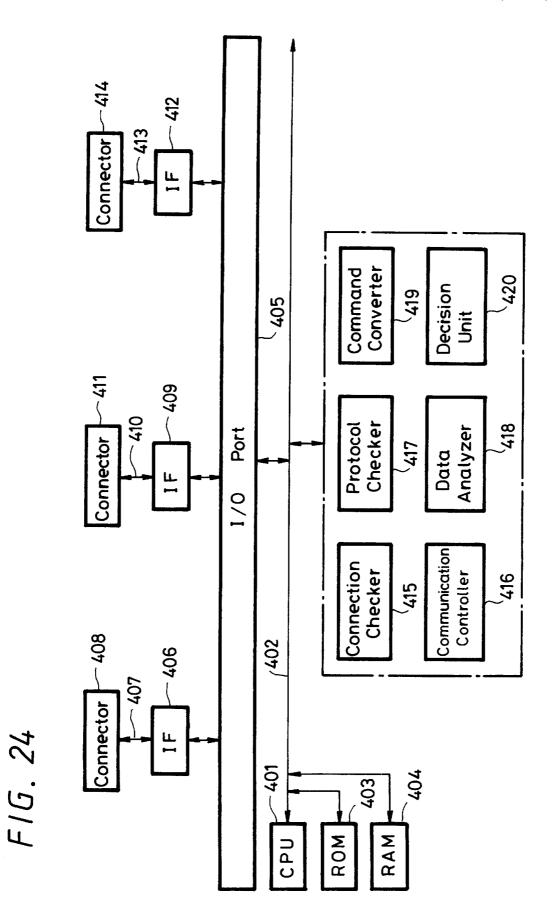

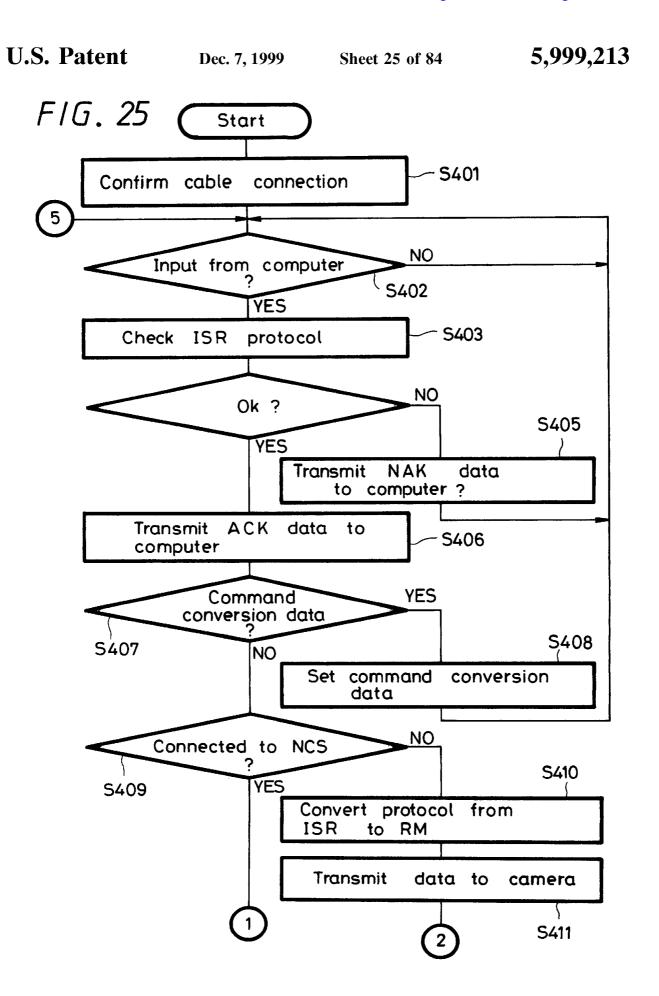

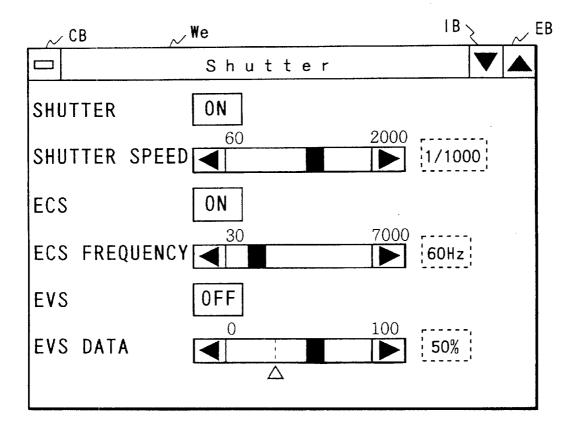

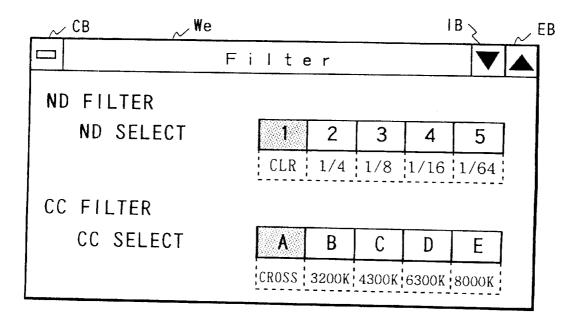

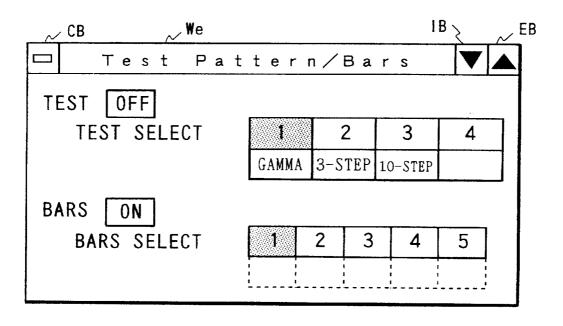

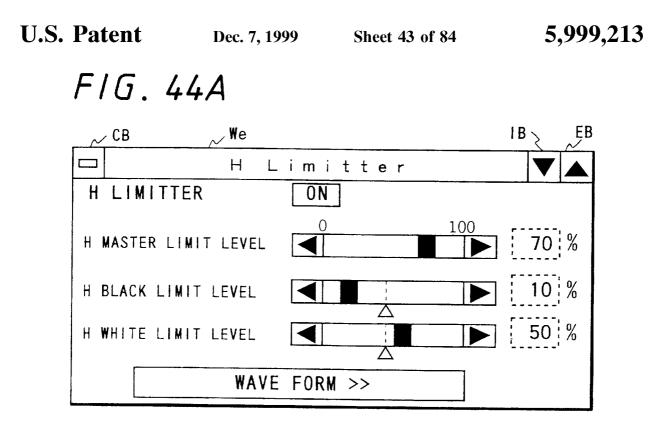

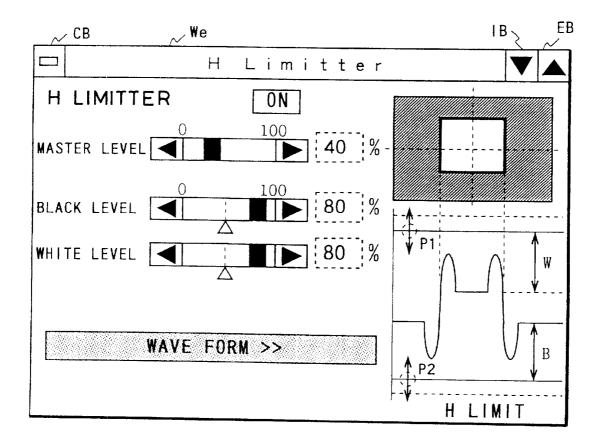

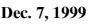

7. 17 On June 4, 1996, the USPTO issued U.S. Patent No. 5,523,795 ("the '795 patent"), entitled "Method and Apparatus for Serial Transmission and/or 18 19 Reception of Nonsynchronous, Multiplexed signals," naming Mamoru Ueda as inventor. A true and correct copy of the '795 patent is attached hereto as Exhibit B. 20 21 8. On December 7, 1999, the USPTO issued U.S. Patent No. 5,999,213 22 ("the '213 patent"), entitled "Method of and Apparatus for Setting up Electronic 23 Device," naming Katsuhiko Tsushima, Kazuyoshi Miyamoto, Taku Kihara, and Yoshio Chiba as inventors. A true and correct copy of the '213 patent is attached 24 25 hereto as Exhibit C.

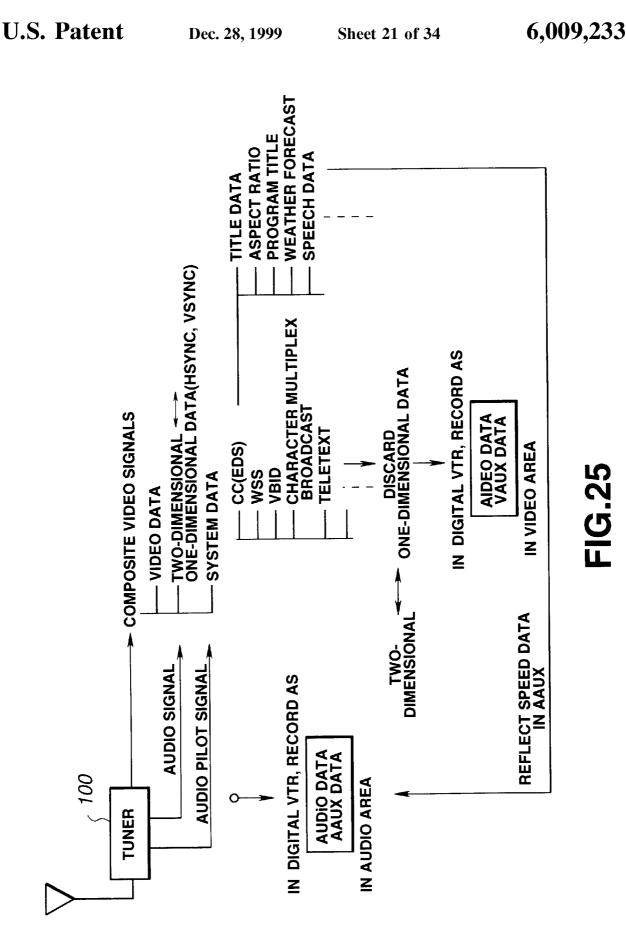

9. On December 28, 1999, the USPTO issued U.S. Patent No. 6,009,233

("the '233 patent), entitled "Apparatus and Method for Recording and Reproducing

a Video Signal With Camera Setting Data," naming Takashi Tsujimura, Terumasa

2

Funabashi, and Chihiro Kaihatsu (now known as Chihiro Motono) as inventors. A true and correct copy of the '233 patent is attached hereto as Exhibit D.

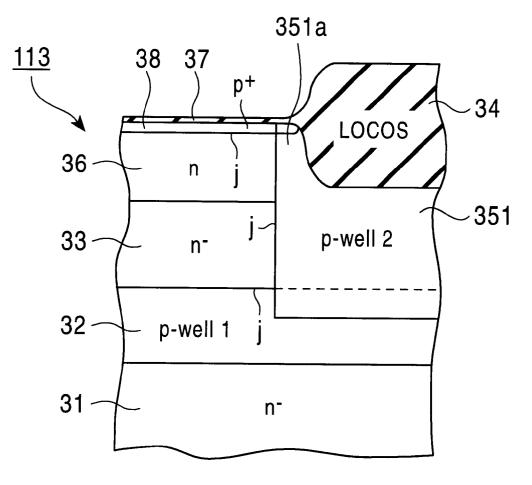

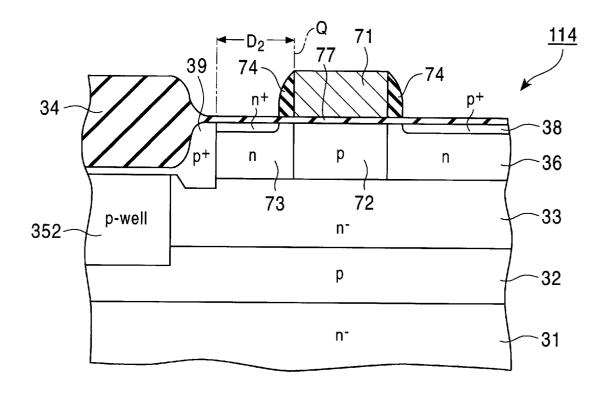

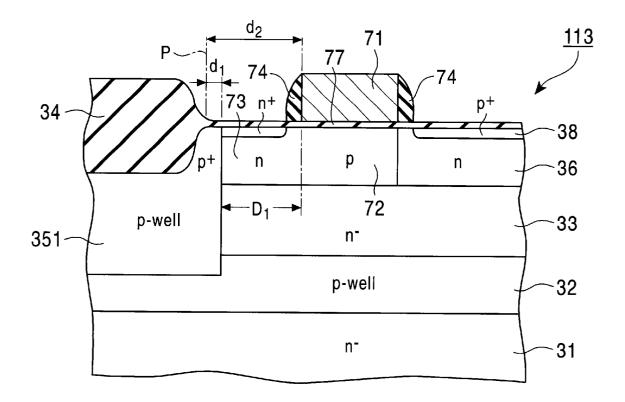

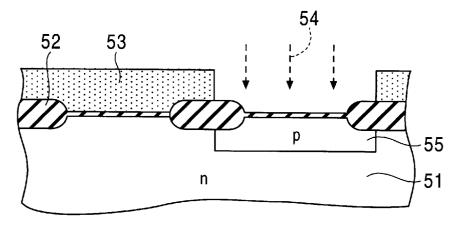

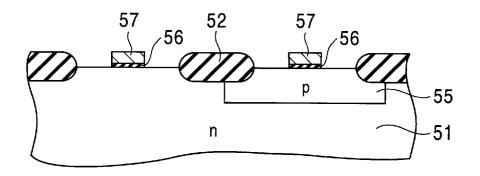

On July 23, 2002, the USPTO issued U.S. Patent No. 6,423,993 ("the

'993 patent"), entitled "Solid-state Image-sensing Device and Method for

Producing the Same," naming Ryoji Suzuki, Takahisa Ueno, Hirofumi Sumi, and

Keiji Mabuchi as inventors. A true and correct copy of the '993 patent is attached

hereto as Exhibit E.

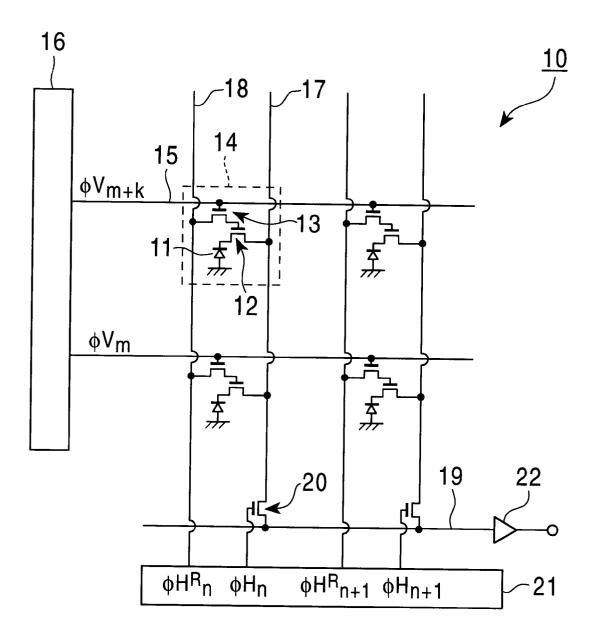

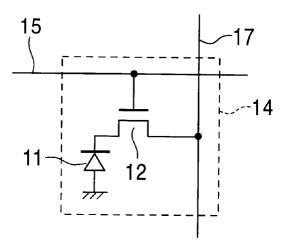

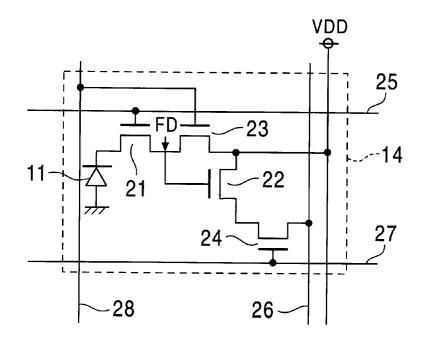

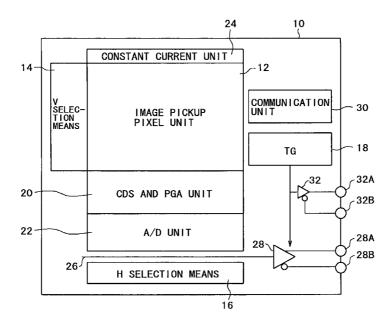

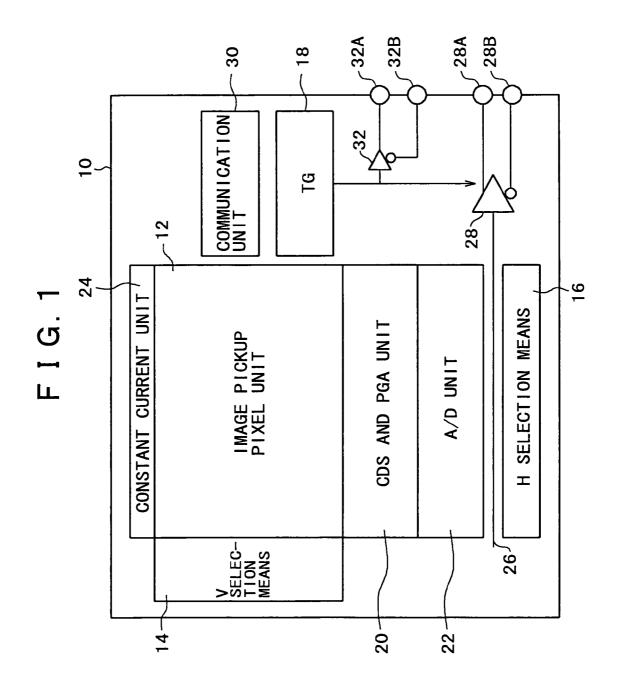

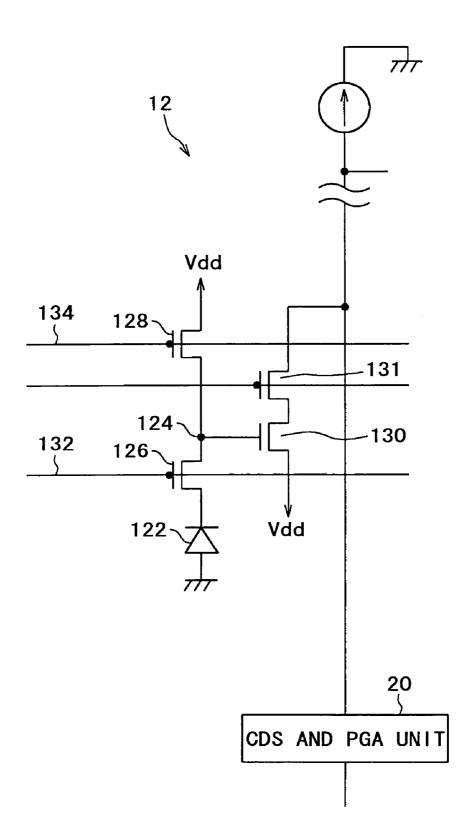

8 11. On November 21, 2006, the USPTO issued U.S. Patent No. 7,138,617

9 ("the '617 patent"), entitled "Solid-state Image Pickup Device and Output Method

10 Thereof," naming Keiji Mabuchi as inventor. A true and correct copy of the '617

11 patent is attached hereto as Exhibit F.

12 12. On December 4, 2007, the USPTO issued U.S. Patent No. 7,304,287 13 ("the '287 patent"), entitled "Solid-state Image Pickup Device and Output Method 14 Thereof," naming Keiji Mabuchi as inventor. On May 20, 2008, the USPTO issued 15 a Certificate of Correction for the '287 patent. A true and correct copy of the '287 16 patent with the certificate of correction is attached hereto as Exhibit G.

17 13. The '718 patent, the '795 patent, the '213 patent, the '233 patent, the

'993 patent, the '617 patent, and the '287 patent are collectively and henceforth

referred to as the "patents-in-suit."

20 14. Sony owns by assignment the entire right, title and interest in and to

21 each of the patents-in-suit with full and exclusive right to sue for past, present, and

22 future infringements thereof.

## 23

1

2

24

# COUNT I: INFRINGEMENT OF THE '718 PATENT

**CAUSES OF ACTION**

25 15. Sony repeats and re-alleges the allegations of the preceding paragraphs

26 of this Complaint as if fully set forth herein.

27 16. Upon information and belief, in violation of 35 U.S.C. § 271, Red has

28 infringed and is continuing to infringe, literally and/or under the doctrine of

equivalents, the '718 patent by practicing one or more claims of the '718 patent in

the manufacture, use, offering for sale, sale, and/or importation of multiple Red

products, including the RED ONE, EPIC, and SCARLET cameras. Sony reserves

the right to contend that additional Red products infringe the '718 patent.

5

17. Red's activities have been without Sony's authorization.

18. As a result of Red's infringement of the '718 patent, Sony has been

damaged, and will be further damaged, and is entitled to be compensated for such

damages pursuant to 35 U.S.C. § 284 in an amount that presently cannot be

ascertained, but that will be determined at trial.

10

## **COUNT II: INFRINGEMENT OF THE '795 PATENT**

11 19. Sony repeats and re-alleges the allegations of the preceding paragraphs

12 of this Complaint as if fully set forth herein.

20. Upon information and belief, in violation of 35 U.S.C. § 271, Red has infringed and is continuing to infringe, literally and/or under the doctrine of equivalents, the '795 patent by practicing one or more claims of the '795 patent in the manufacture, use, offering for sale, sale, and/or importation of multiple Red products, including the RED ONE, EPIC, and SCARLET cameras. Sony reserves the right to contend that additional Red products infringe the '795 patent.

19

21. Red's activities have been without Sony's authorization.

20 22. As a result of Red's infringement of the '795 patent, Sony has been

21 damaged, and will be further damaged, and is entitled to be compensated for such

22 damages pursuant to 35 U.S.C. § 284 in an amount that presently cannot be

23 ascertained, but that will be determined at trial.

24

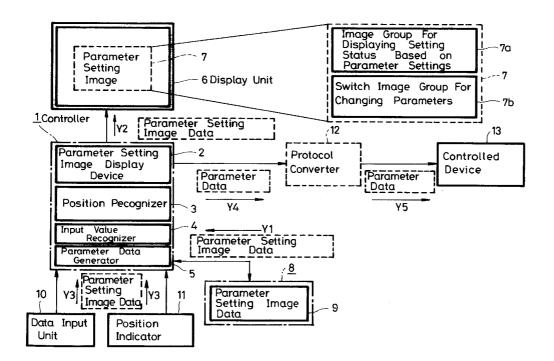

## **COUNT III: INFRINGEMENT OF THE '213 PATENT**

25 23. Sony repeats and re-alleges the allegations of the preceding paragraphs

26 of this Complaint as if fully set forth herein.

27 24. Upon information and belief, in violation of 35 U.S.C. § 271, Red has

28 infringed and is continuing to infringe, literally and/or under the doctrine of

equivalents, the '213 patent by practicing one or more claims of the '213 patent in

the manufacture, use, offering for sale, sale, and/or importation of multiple Red

products, including the REDMOTE, as well as the EPIC and SCARLET cameras.

Sony reserves the right to contend that additional Red products infringe the '213

patent.

6

25. Red's activities have been without Sony's authorization.

As a result of Red's infringement of the '213 patent, Sony has been

damaged, and will be further damaged, and is entitled to be compensated for such

damages pursuant to 35 U.S.C. § 284 in an amount that presently cannot be

ascertained, but that will be determined at trial.

11

## **COUNT IV: INFRINGEMENT OF THE '233 PATENT**

12 27. Sony repeats and re-alleges the allegations of the preceding paragraphs

13 of this Complaint as if fully set forth herein.

Upon information and belief, in violation of 35 U.S.C. § 271, Red has

infringed and is continuing to infringe, literally and/or under the doctrine of

equivalents, the '233 patent by practicing one or more claims of the '233 patent in

the manufacture, use, offering for sale, sale, and/or importation of multiple Red

products, including the SSD MODULE, DSMC SIDE HANDLE, and RED

TOUCH LCD as well as the RED ONE, EPIC, and SCARLET cameras. Sony

reserves the right to contend that additional Red products infringe the '233 patent.

21

29. Red's activities have been without Sony's authorization.

30. As a result of Red's infringement of the '233 patent, Sony has been

damaged, and will be further damaged, and is entitled to be compensated for such

damages pursuant to 35 U.S.C. § 284 in an amount that presently cannot be

ascertained, but that will be determined at trial.

26

## **COUNT V: INFRINGEMENT OF THE '993 PATENT**

31. Sony repeats and re-alleges the allegations of the preceding paragraphs

of this Complaint as if fully set forth herein.

COMPLAINT FOR PATENT INFRINGEMENT

1 32. Upon information and belief, in violation of 35 U.S.C. § 271, Red has 2 infringed and is continuing to infringe, literally and/or under the doctrine of 3 equivalents, the '993 patent by practicing one or more claims of the '993 patent in 4 the manufacture, use, offering for sale, sale, and/or importation of multiple Red 5 products, including the EPIC and SCARLET cameras. Sony reserves the right to 6 contend that additional Red products infringe the '993 patent.

7

33. Red's activities have been without Sony's authorization.

8 34. As a result of Red's infringement of the '993 patent, Sony has been 9 damaged, and will be further damaged, and is entitled to be compensated for such 10 damages pursuant to 35 U.S.C. § 284 in an amount that presently cannot be 11 ascertained, but that will be determined at trial.

12

## **COUNT VI: INFRINGEMENT OF THE '617 PATENT**

35. Sony repeats and re-alleges the allegations of the preceding paragraphs

of this Complaint as if fully set forth herein.

15 36. Upon information and belief, in violation of 35 U.S.C. § 271, Red has

infringed and is continuing to infringe, literally and/or under the doctrine of

equivalents, the '617 patent by practicing one or more claims of the '617 patent in

the manufacture, use, offering for sale, sale, and/or importation of multiple Red

products, including the EPIC and SCARLET cameras. Sony reserves the right to

contend that additional Red products infringe the '617 patent.

21

37. Red's activities have been without Sony's authorization.

38. As a result of Red's infringement of the '617 patent, Sony has been

damaged, and will be further damaged, and is entitled to be compensated for such

damages pursuant to 35 U.S.C. § 284 in an amount that presently cannot be

ascertained, but that will be determined at trial.

26

## **COUNT VII: INFRINGEMENT OF THE '287 PATENT**

39. Sony repeats and re-alleges the allegations of the preceding paragraphs

of this Complaint as if fully set forth herein.

6

40. Upon information and belief, in violation of 35 U.S.C. § 271, Red has

infringed and is continuing to infringe, literally and/or under the doctrine of

equivalents, the '287 patent by practicing one or more claims of the '287 patent in

the manufacture, use, offering for sale, sale, and/or importation of multiple Red

products, including the EPIC and SCARLET cameras. Sony reserves the right to

contend that additional Red products infringe the '287 patent.

7

12

13

41. Red's activities have been without Sony's authorization.

42. As a result of Red's infringement of the '287 patent, Sony has been

damaged, and will be further damaged, and is entitled to be compensated for such

damages pursuant to 35 U.S.C. § 284 in an amount that presently cannot be

ascertained, but that will be determined at trial.

## **PRAYER FOR RELIEF**

WHEREFORE, Sony prays for the following relief:

(a) That the Court enter judgment that Red has infringed each and every

one of the patents-in-suit under 35 U.S.C. § 271 *et seq*;

(b) That the Court enter judgment that Sony has suffered irreparable harm

as a result of Red's infringement, for which there is no adequate remedy at law;

18 (c) That Red, its officers, agents, servants, employees, and those persons acting in active concert or in participation with them be preliminarily and thereafter 19 20 permanently enjoined pursuant to 35 U.S.C. § 283 from making, using, importing, 21 offering to sell, or selling any products that infringe one or more of the patents-in-22 suit, including but not limited to the RED ONE, EPIC, or SCARLET cameras, the SSD MODULE, the DSMC SIDE HANDLE, the REDMOTE, the RED TOUCH 23 5.0" LCD, or the RED TOUCH 9.0" LCD, or otherwise further infringing one or 24 more of the patents-in-suit pursuant to 35 U.S.C. § 283; 25

(d) That Red be required to provide to Sony an accounting of all gains,

profits, and advantages derived by Red as a result of its infringement of the patents-

7 COMPLAINT FOR PATENT INFRINGEMENT

28

| Case | 8:13-cv-00546-JVS-AN Document 1 Filed 04/05/13 Page 9 of 260 Page ID #:12     |  |  |  |  |  |

|------|-------------------------------------------------------------------------------|--|--|--|--|--|

| 1    | in-suit, and that Sony be awarded damages adequate to compensate Sony for the |  |  |  |  |  |

| 2    | wrongful infringing acts by Red, in accordance with 35 U.S.C. § 284;          |  |  |  |  |  |

| 3    | (e) That Red be ordered to pay prejudgment and postjudgment interest;         |  |  |  |  |  |

| 4    | (f) That Red be ordered to pay all costs associated with this action;         |  |  |  |  |  |

| 5    | (g) That Red be directed to deliver up and destroy all infringing products,   |  |  |  |  |  |

| 6    | including but not limited to all RED ONE, EPIC, and SCARLET cameras; and      |  |  |  |  |  |

| 7    | (h) That Sony be granted such other and additional relief as the Court        |  |  |  |  |  |

| 8    | deems just and proper.                                                        |  |  |  |  |  |

| 9    |                                                                               |  |  |  |  |  |

| 10   | DATED: April 5, 2013 Respectfully submitted,                                  |  |  |  |  |  |

| 11   | PROCOPIO CORY, HARGREAVES &                                                   |  |  |  |  |  |

| 12   | SAVITCH LLP                                                                   |  |  |  |  |  |

| 13   | Avit What                                                                     |  |  |  |  |  |

| 14   | By:                                                                           |  |  |  |  |  |

| 15   | Victor M. Felix<br>Mathieu G. Blackston                                       |  |  |  |  |  |

| 16   | 525 B Street, Suite 2200<br>San Diego, CA 92101                               |  |  |  |  |  |

| 17   | Telephone: (619) 238-1900<br>Facsimile: (619) 235-0398                        |  |  |  |  |  |

| 18   | Email: <u>vmf@procopio.com;</u>                                               |  |  |  |  |  |

| 19   | mgb@procopio.com                                                              |  |  |  |  |  |

| 20   | Attorneys for Plaintiff<br>SONY CORPORATION                                   |  |  |  |  |  |

| 21   | OF COUNSEL:                                                                   |  |  |  |  |  |

| 22   | Michael N. Rader                                                              |  |  |  |  |  |

| 23   | Allen S. Rugg<br>Robert M. Abrahamsen                                         |  |  |  |  |  |

| 24   | Charles T. Steenburg<br>Joshua J. Miller                                      |  |  |  |  |  |

| 25   | WOLF GREENFIELD & SACKS, P.C.                                                 |  |  |  |  |  |

| 26   | 600 Atlantic Avenue<br>Boston, MA 02210-2206                                  |  |  |  |  |  |

| 27   |                                                                               |  |  |  |  |  |

| 28   | 8 csteenburg@wolfgreenfield.com; jmiller@wolfgreenfield.com                   |  |  |  |  |  |

| ·    | " 8<br>COMPLAINT FOR PATENT INFRINGEMENT                                      |  |  |  |  |  |

| Case 8   | 13-cv-00546-JVS-AN Document 1 Filed 04/05/13 Page 10 of 260 Page ID #:13      |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------|--|--|--|--|--|

| 1        | DEMAND FOR JURY TRIAL                                                         |  |  |  |  |  |

| 2        | Pursuant to Rule 38 of the Federal Rules of Civil Procedure, Plaintiff hereby |  |  |  |  |  |

| 3        | demands a trial by jury as to all issues so triable.                          |  |  |  |  |  |

| 4        |                                                                               |  |  |  |  |  |

| 5        | DATED: April 5, 2013 Respectfully submitted,                                  |  |  |  |  |  |

| 6        | PROCOPIO CORY, HARGREAVES &                                                   |  |  |  |  |  |

| 7        | SAVITCH LLP                                                                   |  |  |  |  |  |

| 8        | The to the                                                                    |  |  |  |  |  |

| 9        | By: Winter M. F. Li                                                           |  |  |  |  |  |

| 10       | Victor M. Felix<br>Mathieu G. Blackston                                       |  |  |  |  |  |

| 11       | 525 B Street, Suite 2200<br>San Diego, CA 92101                               |  |  |  |  |  |

| 12       | Telephone: (619) 238-1900<br>Facsimile: (619) 235-0398                        |  |  |  |  |  |

| 13       | Email: <u>vmf@procopio.com;</u>                                               |  |  |  |  |  |

| 14       | mgb@procopio.com                                                              |  |  |  |  |  |

| 15       | Attorneys for Plaintiff<br>SONY CORPORATION                                   |  |  |  |  |  |

| 16       |                                                                               |  |  |  |  |  |

| 17       | OF COUNSEL:                                                                   |  |  |  |  |  |

| 18       | Michael N. Rader (BBO #646990)<br>Allen S. Rugg (BBO #674484)                 |  |  |  |  |  |

| 19       | Robert M. Abrahamsen (BBO #636635)                                            |  |  |  |  |  |

| 20       | Charles T. Steenburg (BBO # 663314)<br>Joshua J. Miller (BBO # 685101)        |  |  |  |  |  |

| 21       | WOLF GREENFIELD & SACKS, P.C.<br>600 Atlantic Avenue                          |  |  |  |  |  |

| 22       | Boston, MA 02210-2206<br>Email: Michael.Rader@WolfGreenfield.com;             |  |  |  |  |  |

| 23       | arugg@wolfgreenfield.com; rabrahamsen@wolfgreenfield.com;                     |  |  |  |  |  |

| 24       | csteenburg@wolfgreenfield.com; jmiller@wolfgreenfield.com                     |  |  |  |  |  |

| 25       |                                                                               |  |  |  |  |  |

| 26<br>27 |                                                                               |  |  |  |  |  |

| 27       |                                                                               |  |  |  |  |  |

| 28       | 9                                                                             |  |  |  |  |  |

|          | COMPLAINT FOR PATENT INFRINGEMENT                                             |  |  |  |  |  |

.

Case 8:13-cv-00546-JVS-AN Document 1 Filed 04/05/13 Page 11 of 260 Page ID #:14

# **EXHIBIT A**

Case 8:13-cv-00546-JVS-AN Document 1

# United States Patent [19]

Kobayashi et al.

#### [54] APPARATUS AND METHOD FOR STORING AND REPRODUCING DIGITAL IMAGE DATA YIELDING HIGH RESOLUTION AND HIGH QUALITY VIDEO IMAGE DATA

- [75] Inventors: Hideki Kobayashi; Yasuo Ido, both of Kanagawa, Japan

- [73] Assignee: Sony Corporation, Tokyo, Japan

- [21] Appl. No.: 114,168

- [22] Filed: Sep. 1, 1993

- [30] Foreign Application Priority Data

- Sep. 7, 1992 [JP] Japan ..... 4-264231

- - 358/525; 358/539; 382/233; 382/300

#### [56] References Cited

#### **U.S. PATENT DOCUMENTS**

| 4,660,081 | 4/1987  | Heerah      | 358/160 |

|-----------|---------|-------------|---------|

| 4,823,201 | 4/1989  | Simon et al | 358/133 |

| 5,053,861 | 10/1991 | Tsai et al  | 358/525 |

| 5,065,229 | 11/1991 | Tsai et al  | 358/525 |

\_\_\_\_\_

5,442,718

Aug. 15, 1995

| 5,172,227 | 12/1992 | Tsai et al   | 358/539 |

|-----------|---------|--------------|---------|

| 5,287,188 | 2/1994  | Saeger et al | 348/565 |

#### Primary Examiner-Leo H. Boudreau

Patent Number:

**Date of Patent:**

[11]

[45]

[57]

Attorney, Agent, or Firm-William S. Frommer; Alvin Sinderbrand

#### ABSTRACT

An apparatus for processing image data. The apparatus converts analog green image data signals, analog red image data signals, and analog blue image data signals generated by imaging an object. The third image generation elements, representing the green image data, are arranged at positions shifted by a half pitch to the first and second image generation elements. The analog image data signals are converted into digital image data signals and are then compressed at a predetermined compression rate and stored in a recording medium by a storage means. In reproducing the image data, the recorded image data is read from the recording medium and expanded at a predetermined expansion rate to generate data substantially the same as the image data signals before compression. The expanded data is interpolated in a predetermined interpolation manner.

#### 53 Claims, 7 Drawing Sheets

U.S. Patent

Aug. 15, 1995

Sheet 1 of 7

Exhibit A Page 11 U.S. Patent Aug. 15, 1995 Sheet 2 of 7 5,442,718

-

# FIG. 2

G G G G G G R/B R/B R/B R/B R/B R/B G G G G G G R/B R/B R/B R/B R/B R/B G G G G G G R/B R/B R/B R/B R/B R/B U.S. Patent

Aug. 15, 1995

Sheet 3 of 7

5,442,718

FIG. 3

Exhibit A Page 14

Exhibit A Page 15 U.S. Patent

Aug. 15, 1995

Sheet 6 of 7

5,442,718

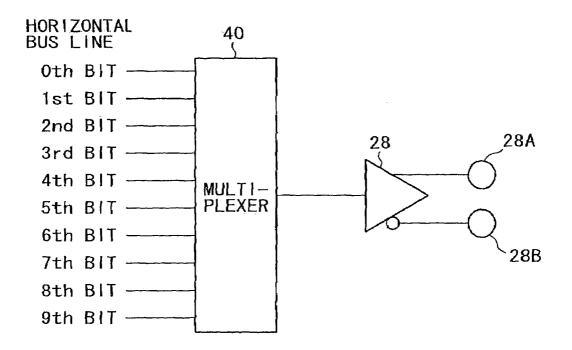

F1G. 6

5,442,718

5

#### APPARATUS AND METHOD FOR STORING AND REPRODUCING DIGITAL IMAGE DATA YIELDING HIGH RESOLUTION AND HIGH QUALITY VIDEO IMAGE DATA

#### BACKGROUND OF THE INVENTION

1. Field of the Invention

The present invention relates to a method of processing image data obtained by an imaging device and to an <sup>10</sup> image data processing apparatus thereof. More particularly the present invention relates to an image data processing apparatus wherein image data is digitally processed and the resultant image data is stored in a recording medium, and to a method thereof. <sup>15</sup>

2. Description of the Related Art

U.S. Pat. No. 4,541,016 discloses an electronic still camera in which an imaging device such as a solid state image sensor generates analog image data and the generated analog image data is recorded on a magnetic disc <sup>20</sup> in an analog signal form. Such electronic still cameras provide a picture of the same as quality that in silverhalide-photography type cameras. Since the image data is recorded on a magnetic disc, the imagery produced by the electronic still camera inevitably suffers from <sup>25</sup> jitter and resultant color stain (mixture). As a result, the reproduced image it suffers from the disadvantages of a low resolution and a low quality of the picture. Also, it suffers from the disadvantage of a large memory capacity required for storing the analog image data. <sup>30</sup>

#### SUMMARY OF THE INVENTION

An object of the present invention is to provide a method of processing image data by which generation of jitter in processed image data and the resultant color <sup>35</sup> stain (mixture) in the picture are prevented and to thereby to provide pictures of a high resolution and a high quality.

Another object of the present invention is to provide a method of processing image data which enables stor- 40 age of a large amount of original image data with a small memory.

Still another object of the present invention is to provide an image processing apparatus using the above methods. 45

According to the present invention, there is provided an apparatus for processing an image data signal formed by at least three color components, including a conversion unit for converting analog intensities of the color component data of the image data signal to digital inten-50 sity color component data, a compression unit for compressing the digital color component data of the image data signal converted by the conversion unit at a predetermined rate including a compression rate of 1/1, and a storage unit for storing the compressed digital color 55 component data of the image data signal by the compression means in a digital recording medium.

Further, according to the present invention, there is provided an apparatus for processing image data signal which has moreover a data reading unit for reading the 60 digital color component data of the image data signal from the recording medium, an expansion unit for expanding the digital color component data of the image data signal read from the recording medium at a predetermined expansion rate, to reproduce expansion data 65 substantially the same as the data before the compression, and an interpolating unit for generating data interpolating the digital color component data of the image

data signal expanded by the expansion unit in a predetermined interpolation manner, to thereby provide reproduction image picture data having a predetermined resolution.

Further, according to the present invention, there is provided an apparatus for processing image data signal formed by at least three color components including a conversion unit for converting analog intensities of the color component data of the image data signal to digital intensity color component data, an interpolating unit for interpolating the digital color component data of the image data signal converted by the conversion unit by a predetermined interpolation manner, a compression unit for compressing the digital color component data of the image data signal interpolated by the interpolating unit at a predetermined rate including a compression rate of 1/1, and a storage means for storing the compressed digital color component data of the image data signal by the compression unit in a digital recording medium.

Further, according to the present invention, there is provided an apparatus for processing image data signal which has moreover a data reading unit for reading the digital color component data of the image data signal from the recording medium, and an expansion unit for expanding the digital color component data of the image data signal read from the recording medium at a predetermined expansion rate, to reproduce expansion data substantially the same as the data before the compression, to thereby provide reproduction image picture data having a predetermined resolution.

Further, according to the present invention, there is provided a method of processing an image data signal formed by at least three color components, which include the steps of converting analog intensities of the color component data of the image data signal to digital intensity color component data, compressing the digital color component data of the converted image data signal at a predetermined rate including a compression rate of 1/1, and storing the compressed digital color component of the image data signal by the compression means to a digital recording medium.

Further, according to the present invention, there is provided the method of processing an image data signal which includes moreover the steps of reading the digital color component data of the image data signal from the recording medium, expanding the digital color component data of the image data signal read from the recording medium at a predetermined expansion rate to reproduce expansion data substantially the same as the data before the compression, and generating data interpolating the expanded digital color component data of the image data signal in a predetermined interpolation manner, to thereby provide reproduction image picture data having a predetermined resolution.

Further, according to the present invention, there is provided a method of processing an image data signal formed by at least three color components, which includes the steps of converting analog intensities of the color component data of the image data signal to digital intensity color component data, generating data interpolating digital color component data on the basis of the converted digital color component data of the image data signal in a predetermined interpolation manner, compressing the interpolated digital color component data of the image data signal at a predetermined rate including a compression rate of 1/1, and storing the

> Exhibit A Page 18

5,442,718

compressed digital color component of the image data signal in a digital recording medium.

Further, according to the present invention, there is provided the method of processing an image data signal which includes moreover the steps of reading the digital 5 color component data of the image data signal from the recording medium, and expanding the digital color component data of the image data signal read from the recording medium at a predetermined expansion rate, to reproduce expansion data substantially the same as the 10 data before the compression, to thereby provide reproduction image picture having a predetermined resolution.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The above objects and features and other objects and features of the present invention will become clearer by the following description with reference to accompanying drawings, wherein:

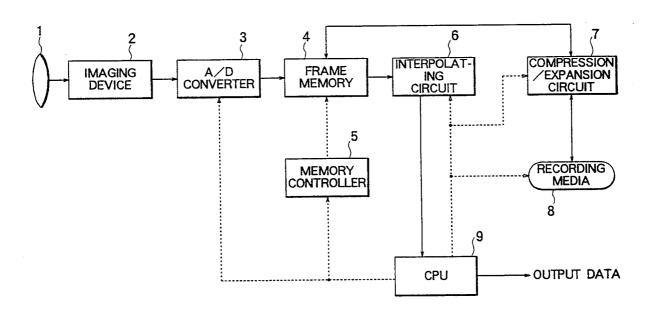

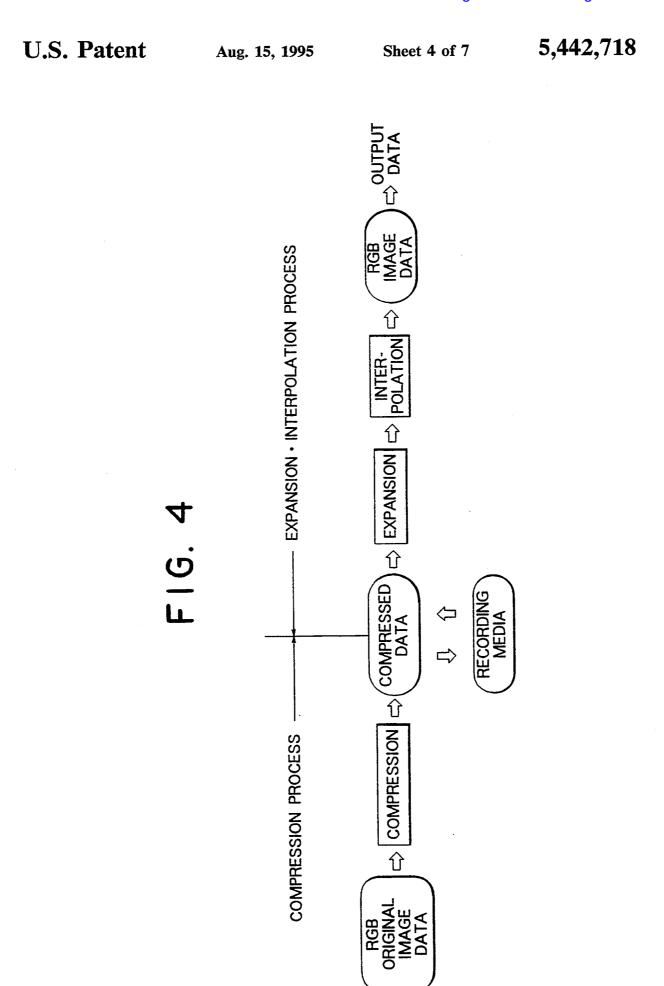

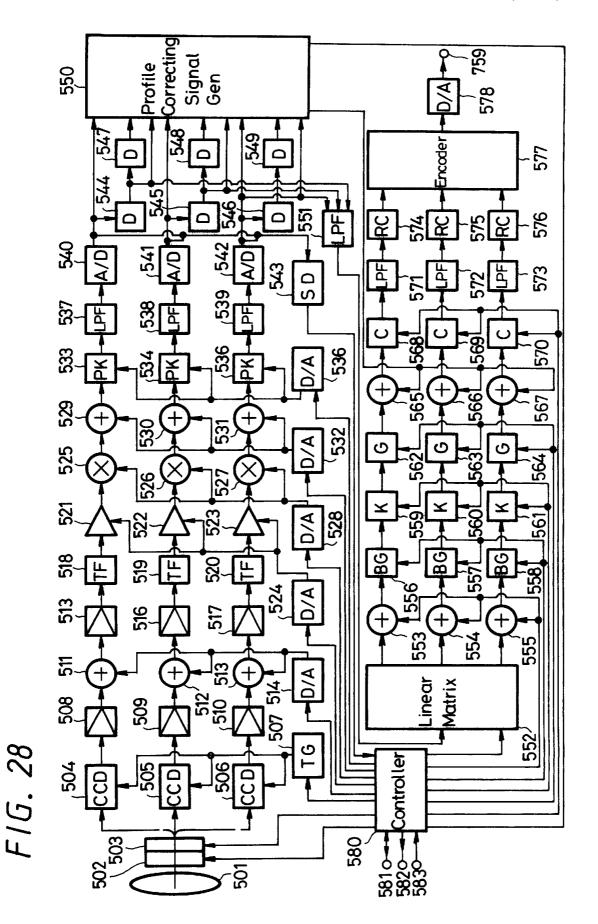

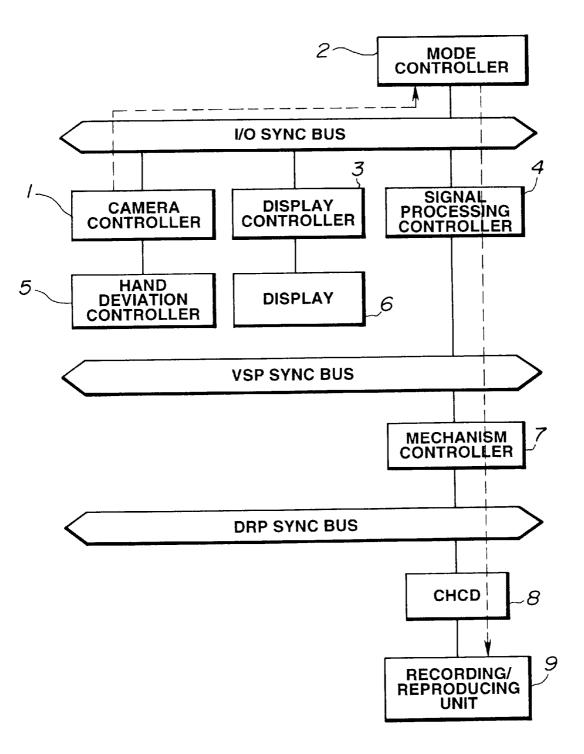

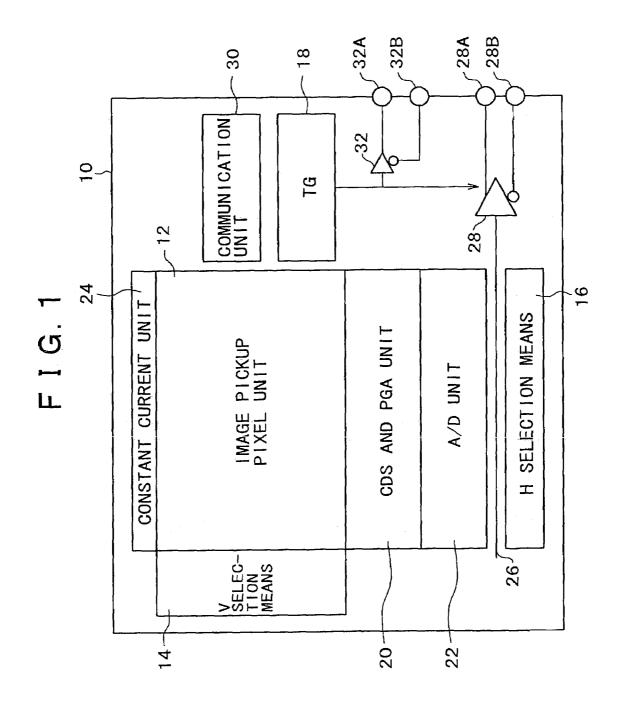

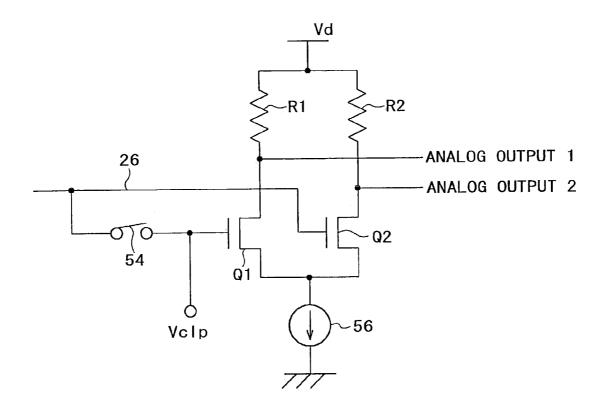

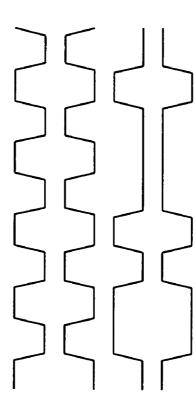

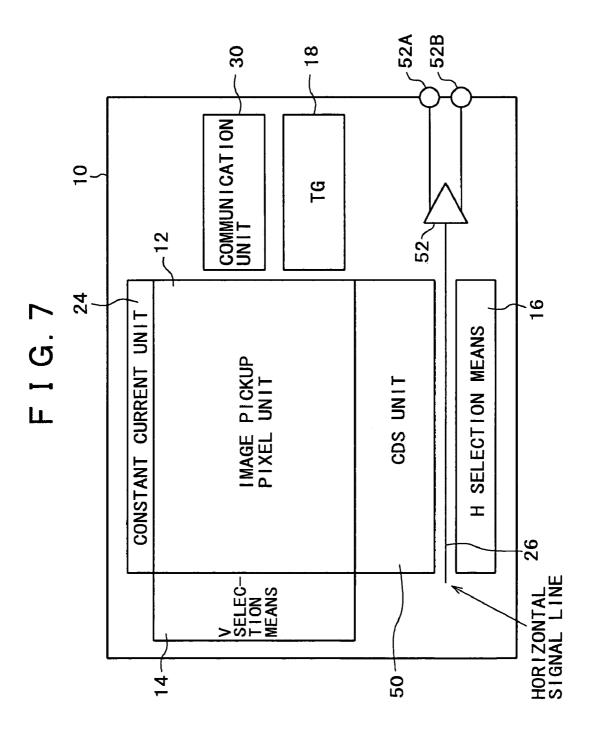

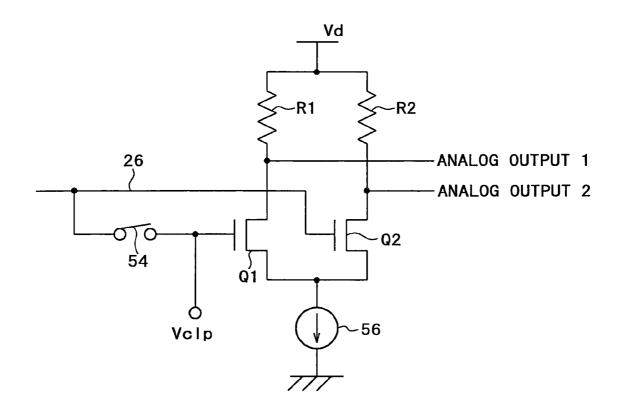

FIG. 1 is a block diagram showing a first embodiment 20 of an image data processing apparatus according to the present invention;

FIG. 2 is a view for explaining how three elementary colors can be generated by an imaging device of the image data processing apparatus in FIG. 1;

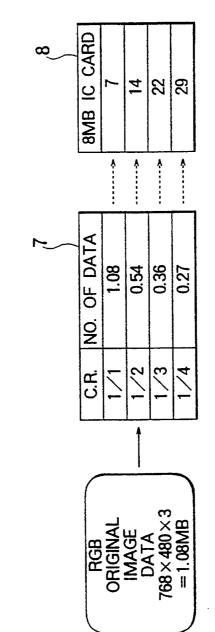

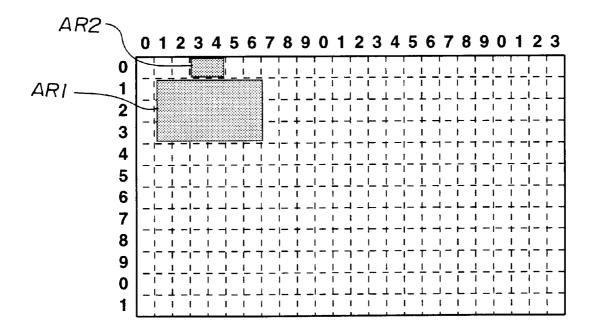

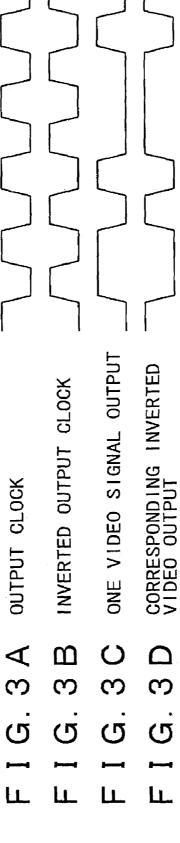

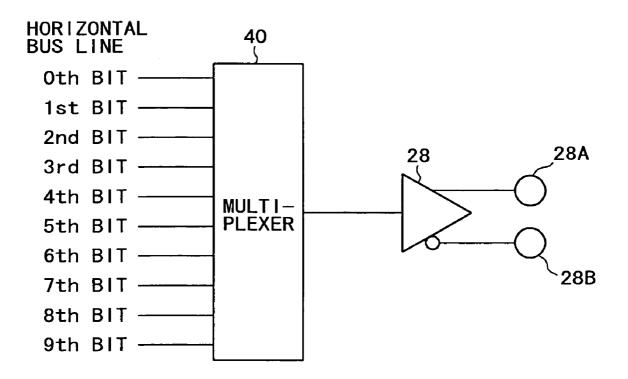

FIG. 3 is a view for explaining the relationship among a compression rate, the amount of compressed data, and the number of pictures recorded in a recording medium in the image data processing apparatus in FIG. 1;

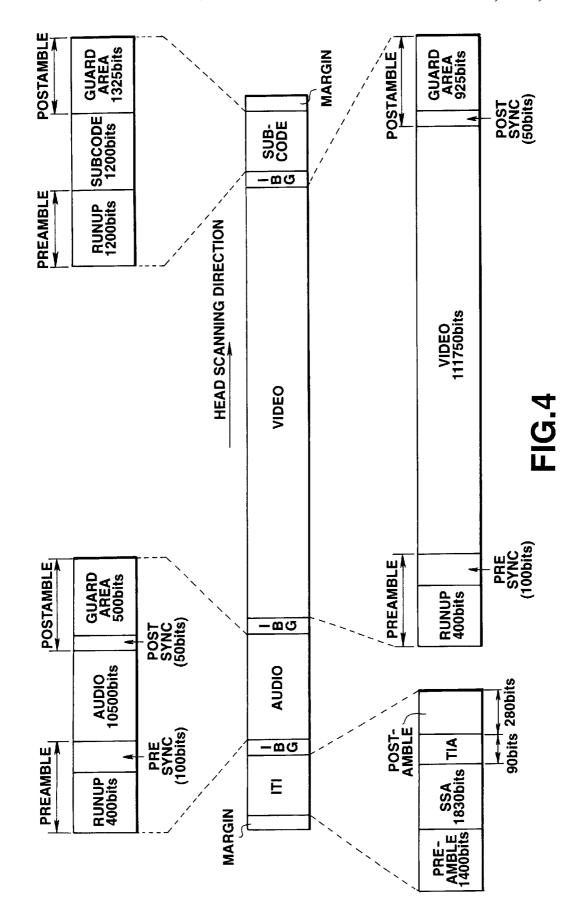

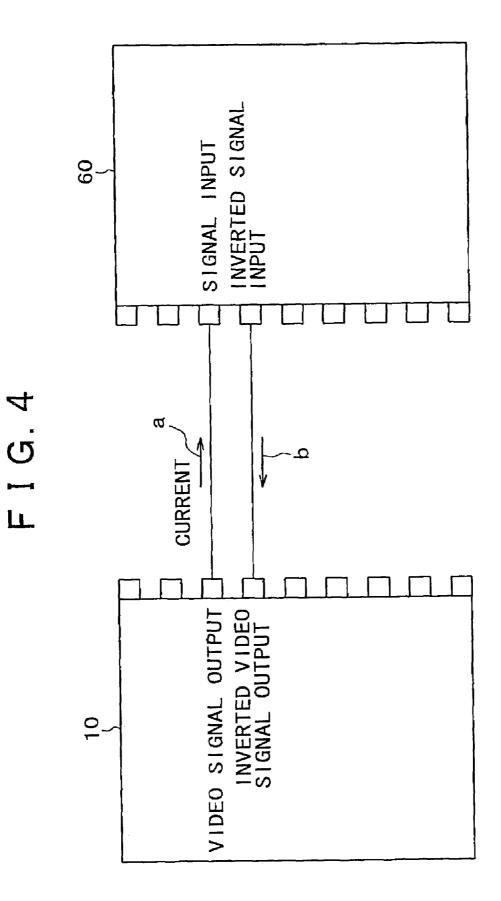

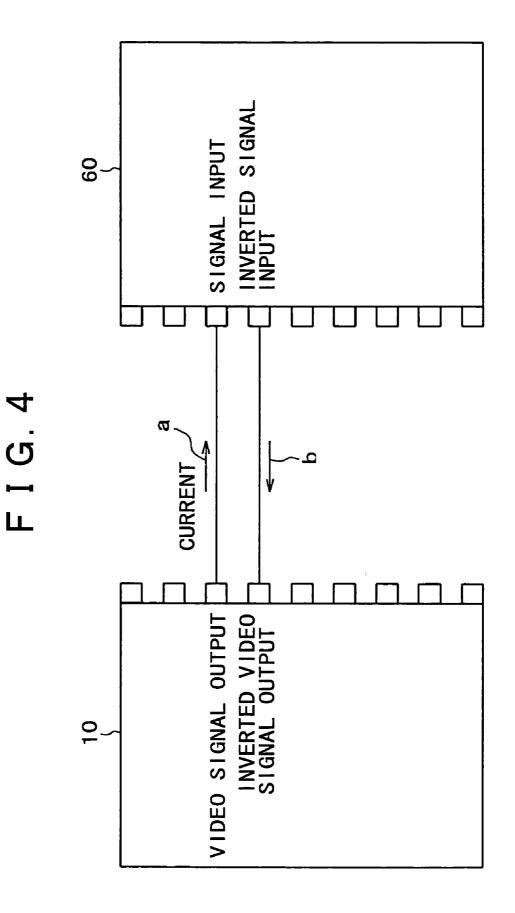

FIG. 4 is a view for explaining operations of the image data processing apparatus in FIG. 1;

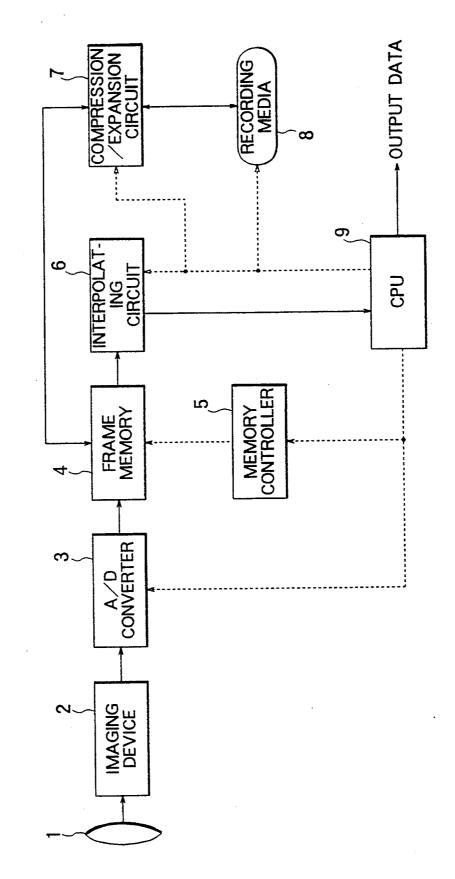

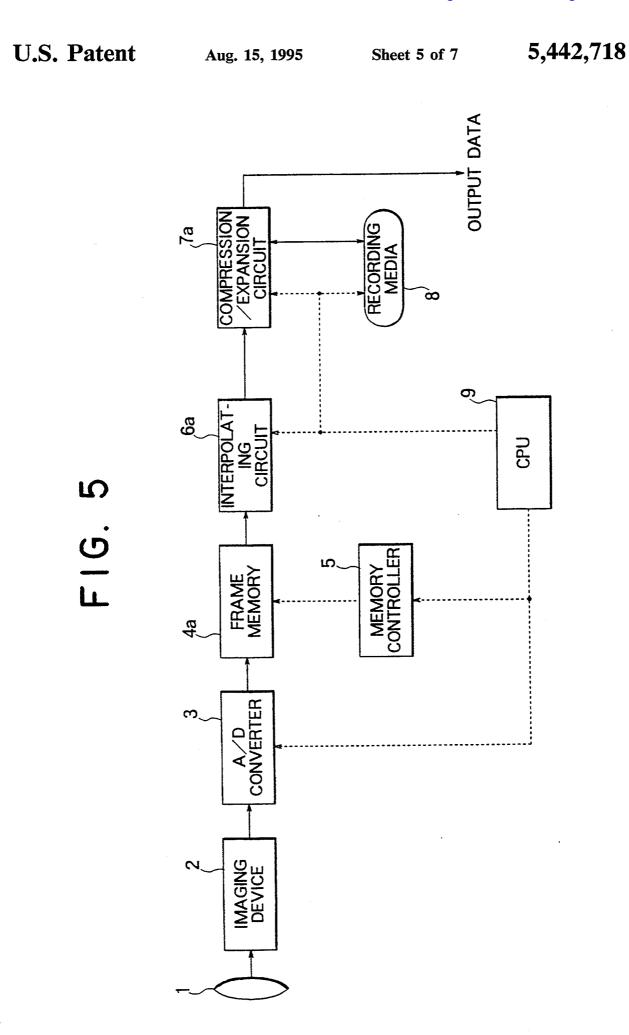

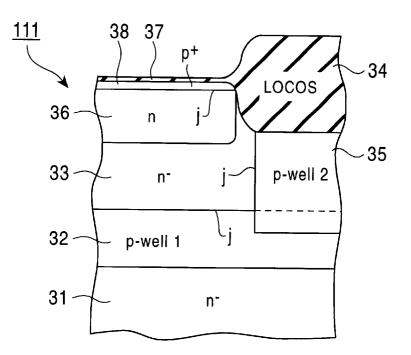

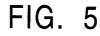

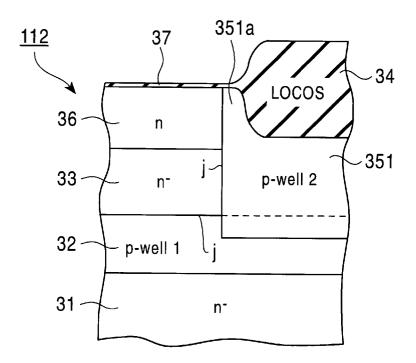

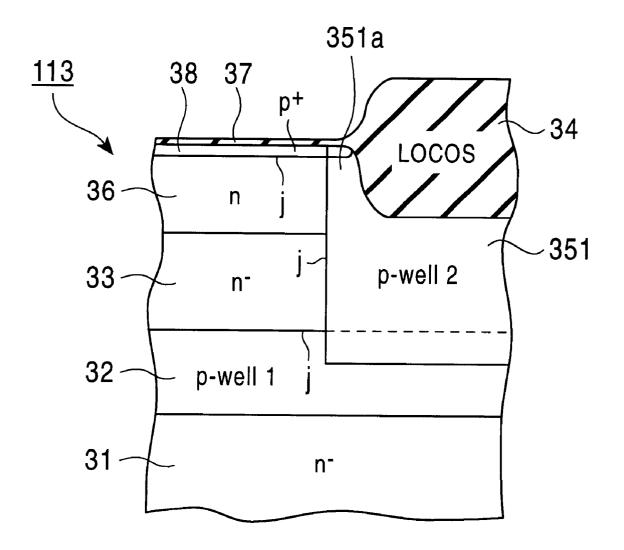

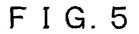

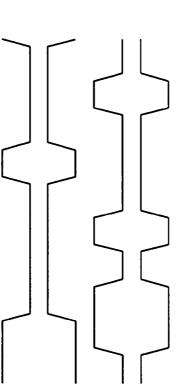

FIG. 5 is a block diagram showing a second embodiment of an image data processing apparatus according to the present invention:

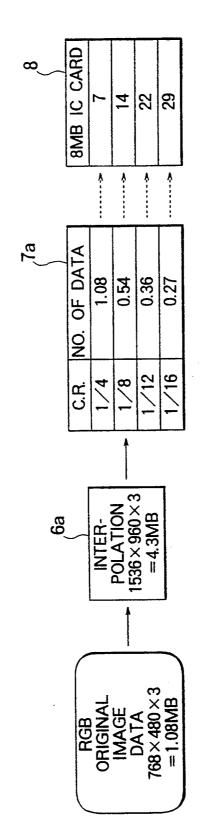

FIG. 6 is a view for explaining the relationship among a compression rate, the number of compressed data, and the amount of picture recorded in a recording media in the image data processing apparatus in FIG. 5, and

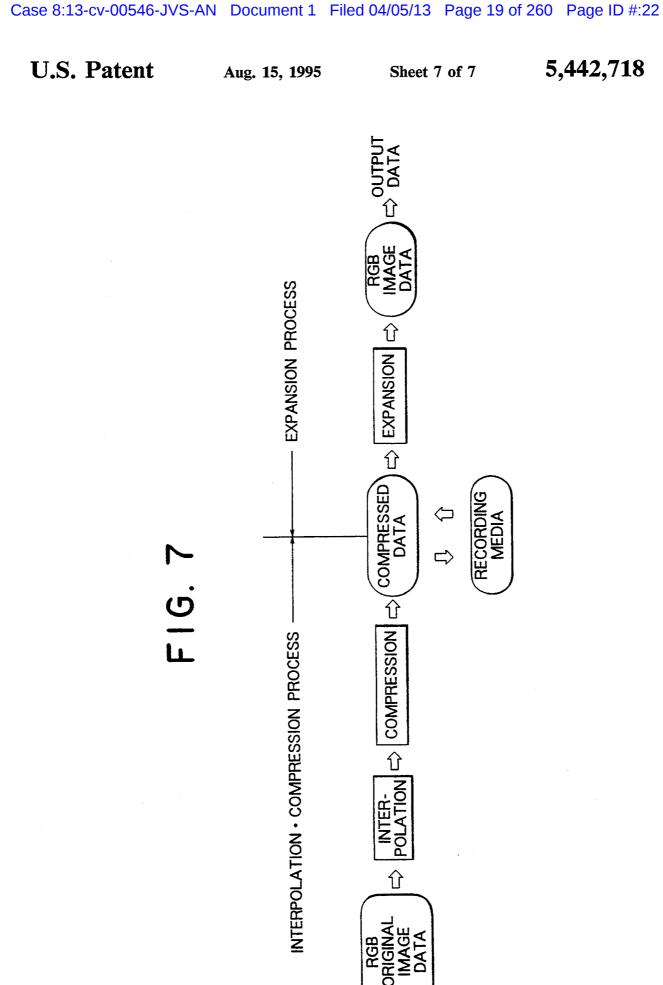

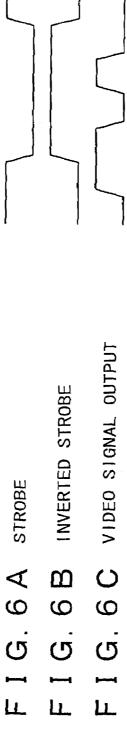

FIG. 7 is a view for explaining operations of the image data processing apparatus in FIG. 5.

#### DESCRIPTION OF THE PREFERRED EMBODIMENTS

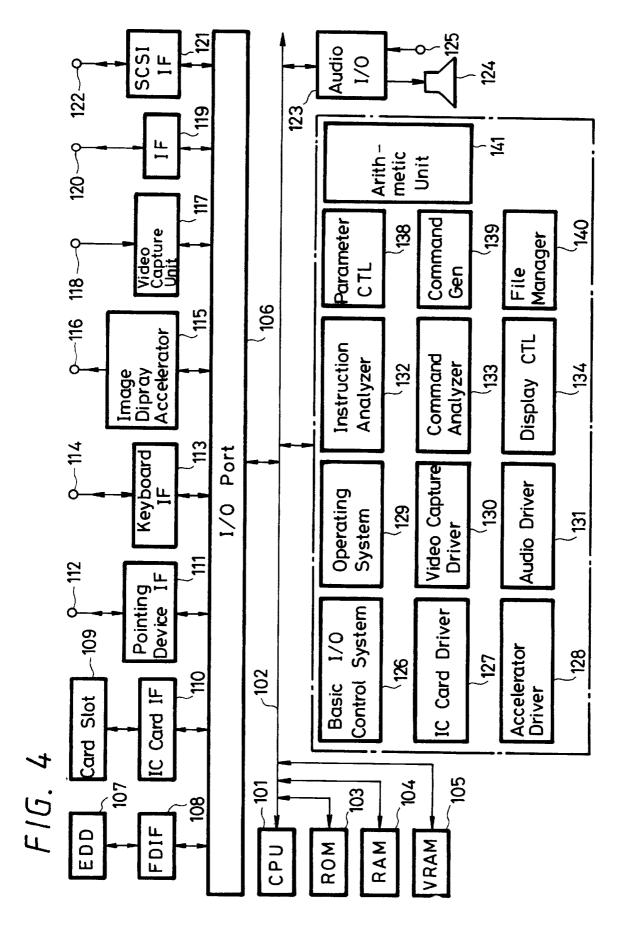

FIG. 1 is a block diagram showing a first embodiment of an image data processing apparatus, built in a digital electronic still camera, according to the present invention.

In FIG. 1, 1 denotes an image formation lens, 2 an 50 imaging device, 3 an analog/digital converter (A/D converter), 4 a frame memory, 5 a memory controller, 6 an interpolating circuit, 7 a data compression/expansion circuit, 8 a recording medium, and 9 a central processing unit (CPU).

The image formation lens 1 condenses light from an object not shown, and forms an image at an appropriate position of the imaging device 2.

The imaging device 2, for example, has a three plates type charge coupled device (CCD) which is provided 60 with a plurality of R-CCDs, a plurality of G-CCDs, and plurality of B-CCDs, generates analog electric color signals of red(R), green(G), and blue(B), i.e., the three primary colors, according to a quantity (an intensity) of the received light, and outputs an analog image data on 65 the above described DCT compression process. the basis of the intensity of the generated color signal.

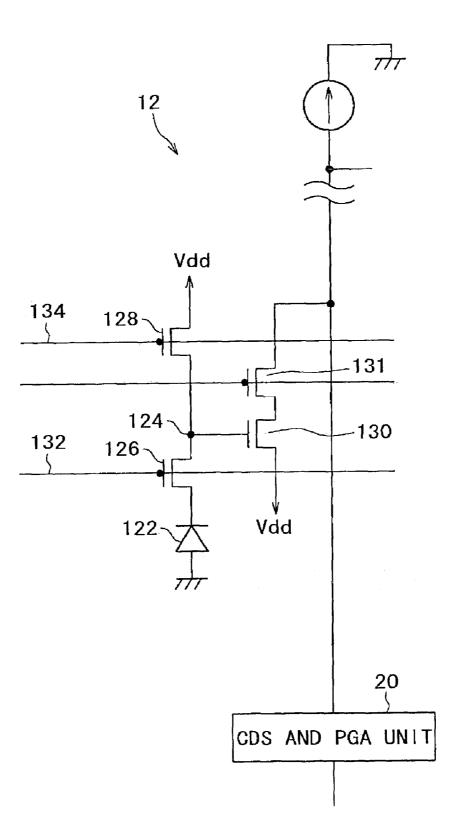

As shown in FIG. 2, in the three plate type CCD imaging device 2 of this embodiment, the G-CCDs are

arranged at positions offset from the lattice of the R-CCDs and the B-CCDs. Specifically, the G-CCDs are arranged so that the pixel portions are shifted by a half pitch from the registration position of the R-CCDs and B-CCDs the in both horizontal and the vertical directions. In this embodiment, the R-CCDs and the B-CCDs are arranged at the same positions. This technology is disclosed in, for example, Japanese Unexamined Patent Publication (Kokai) 2(1990)-177672.

The A/D converter 3 converts red color analog intensities of the image data signal, blue color analog intensities of the image data signal, and green color analog intensities of the image data signal which are obtained from the imaging device 2, to digital intensity 15 signals.

The frame memory 4 stores the image data which is converted to the digital signals by the A/D converter 3. The data is subjected to an expansion process in the data compression/expansion circuit 7, under the control of the memory controller 5.

The interpolating circuit 6 performs interpolation on the basis of the shift of the digital image data G which had been offset in the horizontal and vertical directions, which was output from the data compression/expan-25 sion circuit 7 and stored in the frame memory 4. For example, when original image data of (768 $\times$ 480 $\times$ 3) pixels and a memory size thereof is 1.08 megabytes, according to the interpolation, high definition image data of  $(1536 \times 960 \times 3)$  pixels are obtained and a mem-30 ory size thereof is 4.3 megabytes.

As shown in FIG. 2, the interpolating circuit 6 performs interpolation of the image data to produce image data arranged in spaces, each positioned between the red and blue image data position, and the green image 35 data position.

In the compression process, the data compression/expansion circuit 7 compresses the original image data of  $(768 \times 480 \times 3)$  pixels of 1.08 megabytes stored in the frame memory 4 in compression process, at a predeter-40 mined compression rate, for example 1/1 (no compression), 1/2, 1/3, 1/4... The compressed image data is stored in the recording medium 8 under control of the CPU 9.

The compression in the compression/expansion cir-45 cuit 7 uses, for example, a two-dimensional discrete cosine transformation (DCT).

In the DCT method, for example, the digital image data in the frame memory 4 is divided into a plurality of blocks of  $N \times N$  pixels. The data in the block is subjected to the two dimensional DCT, and the  $N \times N$  pixel data is converted to N×N DCT transformed pixel data. The N×N DCT transformed data is quantized using a predetermined quantization table at a different step size for each coefficient position. The quantized data is 55 coded to result in the compressed data.

Also, in the expansion-interpolation process, the data compression/expansion circuit 7 expands the compressed image data read from the recording medium 8 under the control of the CPU 9 at a predetermined expansion rate to restore the original image data. The compressed image data is converted to a picture signal of a predetermined format, and stores the picture signal is stored in the frame memory 4.

The expansion process includes a process reverse of

The recording medium 8 records the image data compressed in the data compression/expansion circuit 7 under the control of the CPU 9 in the compression process. And in the expansion-interpolation process, the recorded image data is read from the recording medium, and output to the data compression/expansion circuit 7 under the control of the CPU 9.

FIG. 3 shows the relationship among a compression 5 rate, the amount of compressed data, and the number of pictures recorded in the recording mediums, for example, an integrated circuit (IC) card which includes a microprocessor for signal processing and a semiconductor memory for storing the compressed image data. If 10 the IC card is portable, and then the IC card can be loaded on another apparatus for reproducing the image data.

As shown in FIG. 3, since the digital image data is compressed at a predetermined compression rate in the 15 compression/expansion circuit 7, it is possible to store the reduced digital compression image data to the IC card.

In the embodiment, since the compression is performed prior to the predetermined interpolation pro- 20 cess, it is possible to increase the compression rate compared with compression after interpolating. Also, it is also possible to increase the number of pictures able to be stored in the IC card by increasing the compression rate. 25

The CPU 9 controls the transmission and reception of data between the frame memory and the data compression/expansion circuit 7 and between the compression/expansion circuit 7 and the recording medium 8. Also, the CPU 9 converts the image data output from the 30 interpolating circuit 6 to a high definition picture signal having a predetermined format and outputs the picture signal as RGB image data.

Next, the operation by the above-described structure will by explained referring to FIG. 1 and FIG. 4.

Light from an object, not shown, is input to the image formation lens I and forms an image at an appropriate position of the imaging device 2. In the imaging device 2, a red color analog signal, blue color analog signal, and green color analog signal are generated according 40 to the quantity (intensity) of the received light. These signals are subjected to a predetermined signal processing, and are output to the A/D converter 3 as the analog image data signal. As described above, the analog image data of the G-CCDs are shifted by a half pitch in 45 the horizontal and vertical directions from a registration position of the R-CCDs and the B-CCDs.

In the A/D converter 3, the input red color analog image data, blue color analog image data, and green color analog image data are converted to red color 50 digital image data, blue color digital image data, and green color digital image data, respectively. This digital image data is stored in the frame memory 4 as the RGB original image data.

The image data stored in the frame memory 4 of 55  $(768 \times 480 \times 3)$  pixels of 1.08 megabytes is read and output to the data compression/expansion circuit 7.

In the data compression/expansion circuit 7, the red color digital image data, the blue color digital image data, and the green color digital image data are subjected to a predetermined compression process at a predetermined compression rate, or are held as is, without compressed or the non compressed image data are stored in the recording medium 8 under the control of 65 the CPU 9.

When outputting the image data stored in the recording medium 8 to a display like a liquid crystal device or 6

a printer, the desired red color digital image data, blue color image data, and green color image data are read from the appropriate recording areas of the recording medium 8 and output to the data compression/expansion circuit 7 under the control of the CPU 9.

In the data compression/expansion circuit 7, the compressed image data read from the recording medium 8 is expanded to restore it to the original image data at a predetermined expansion rate. The expanded image data is stored in the frame memory 4. The expanded image data stored in the frame memory 4 is read out and output to the interpolating circuit 6.

In the interpolating circuit 6, as the G data of the RGB original image data is shifted by a half pitch in the horizontal and vertical directions, the G data of the RGB original image data is subjected to interpolation on the basis of that shift, and then is output to the CPU 9 as image data of  $(1536 \times 960 \times 3)$  pixels of 4.3 megabytes.

In the CPU 9, the input image data is converted to picture signals having a predetermined format. The picture signals are output as RGB image data.

As explained above, according to the present embodiment, the electronic still camera obtains the analog pixel image data, converts the same to digital pixel image data, compresses the digital image data at a predetermined compression rate and stores the recording medium 8. In outputting the image data from the recording medium 8, the invention expands the stored image data, interpolate the expanded image data, and then output the interpolated image data. Due to this operation, it is possible to prevent the generation of jitter and the resultant color-stain and thus high resolution and high qual-35 ity pictures are obtain.

Also, as the A/D converted image data is compressed directly, and the compressed image data is stored in the recording medium 8, therefore, when the IC card is used as the recording medium 8, it is possible to store a number of sets of image data on a single IC card and thus obtain a practical, broad-use apparatus.

Also, it is possible to perform interpolation of the digital image data, compress the interpolated digital image data, and then store the compressed image data in the recording medium 8. Alternatively, in the present embodiment, it is possible to increase the compression rate and, thereby reduce the time for the compression process, as compared with compression after interpolation.

It should be noted that, in the present embodiment, the imaging device required the the case of shifting of the positions of the pixels of three sets of CCD's in the horizontal and vertical directions as shown in FIG. 2 and the performing of a high definition signal process (interpolation process) to obtain high picture quality images. However, the present invention can be applied even to cameras with one or two set of CCD's by shifting the pixels in just one direction, such as the horizontal direction.

Also, in the present embodiment was explained using a DCT as the method at compression and an inverse DCT as the method of expansion. However, the present invention can also be applied to other a variety of coding and decoding methods for the compression and the expansion of data

Further, the present embodiment was explained through the use of the IC card as the recording medium. However, the present invention can also be applied to a 5,442,718

7 portable static memory card, a floppy disk, or other recording medium.

The present invention can also be applied even to the use of a portable recording medium, which can be loaded on another digital electronic still camera to 5 move compressed digital image data and compression rate data thereon. When it is loaded in another electronic still camera, the compressed digital image data and compression rate data are read from the loaded recording medium. The read data is expanded in the 10 data compression/expansion circuit at an expansion rate based on the stored compression rate data to reproduce expansion data substantially the same as the data before compression. The expanded data is interpolated in a predetermine interpolation manner to generate picture 15 and vertical directions from the registration position of signals, and the picture signals are output as RGB image data.

FIG. 5 is a block diagram showing a second embodiment of an image data processing apparatus according to the present invention.

Note that, in FIG. 5, the reference numerals are the same as shown in FIG. 1 and indicate the same component of the apparatus. Therefore, explanation of these components is omitted.

digital signals by the A/D converter 3 under the control of the memory controller 5.

The interpolating circuit 6a performs the interpolation to shift the digital image data G, output from the A/D converter 3 and stored in the frame memory 4a, 30 the horizontal and vertical directions. Original image data of  $(768 \times 480 \times 3)$  pixels and 1.08 megabytes would thus obtain the high definition image data of  $(1536 \times 960 \times 3)$  pixels of 4.3 megabytes.

The interpolation in the interpolating circuit 6a is as 35 same as in the interpolating circuit 6 in FIG. 1.

The data compression/expansion circuit 7a compresses the 4.3 megabyte image data which is interpolated in the interpolating circuit 6a, at a predetermined compression rate, for example, 1/4, 1/8, 1/12, 1/16 ... 40 the control of the CPU 9. The compressed image data is stored in the recording medium 8.

In the expansion process, the data compression/expansion circuit 7a expands the compressed image data read from the recording medium 8 under the control of 45 from the appropriate recording areas of the recording the CPU 9 at a predetermined expansion rate to restore the original image data, converts the image data to picture signals of a predetermined format, and outputs the picture signals as the RGB image data.

compression/expansion circuit 7a is the same as the data compression/expansion circuit 7 in FIG. 1.

The recording medium 8 records the image data compressed in the data compression/expansion circuit 7a under the control of the CPU 9. In the expansion pro- 55 ment, the electronic still camera produces the analog cess, the recorded image data is read from the recording medium 8 and output to the data compression/expansion circuit 7a under the control of the CPU 9.

FIG. 6 shows the relationship among a compression rate, the amount of compressed data and the number of 60 pictures recorded in the recording medium 8, e.g., an 8 megabyte IC card.

As shown in FIG. 6, since the digital image data is compressed at a given compression rate in the compression/expansion circuit 7a and the compressed image 65 directly and the compressed image data is stored in the data is recorded in the recording medium 8, it is possible to store a plurality of the picture data on the IC card. Also, it is possible to expand the quantity of picture data

stored on the IC card by more increasing the compression rate.

Next, the operation by the above-described structure will be explained referring to FIG. 5 and FIG. 7.

Light from an object, not shown, is input to the image formation lens I and forms an image at an appropriate position of the imaging device 2. In the imaging device 2, a red color analog signal, blue color analog signal, and green color analog signal are generated according to the quantity (intensity) of light received. These signals are subjected to predetermined processing, and are output to the A/D converter 3 as the analog image data signal. As described above, these analog image data of the G-CCDs are shifted by a half pitch in the horizontal the R-CCDs and B-CCDs.

In A/D converter 3, the input red color analog image data, blue color analog image data, and green color analog image data are converted to red color digital 20 image data, blue color digital image data, and green color digital image data, respectively. This digital image data 13 stored in the frame memory 4a as the RGB original image data.

The image data stored in the frame memory 4a of The frame memory 4a stores image data converted to 25 (768×480×3) pixels of 1.08 megabytes is read, and output to the interpolating circuit 6a.

In the interpolating circuit 6a, as the G's of the RGB original image data are shifted in the horizontal and vertical directions, the G's of RGB original image data are subjected to interpolation on the basis of the position shift, and then output to the data compression/expansion circuit 7a as image data of  $(1536 \times 960 \times 3)$  pixels of 4.3 megabytes.

In the data compression/expansion circuit 7a, the red color digital image data, the blue color digital image data, and the green color digital image data are subjected to a predetermined compression process at a predetermined compression rate. The compressed image data is stored in the recording medium 8 under

When outputting the image data stored in the recording medium 8 to a display like a liquid crystal device or a printer, the desired red color digital image data, blue color image data, and green color image data are read medium 8 and output to the data compression/expansion circuit 7*a* under the control of the CPU 9.

In the data compression/expansion circuit 7a, the compressed image data read from the recording me-The compression and expansion operation of the data 50 dium 8 13 expanded to restore it to the original image data at a predetermined expansion rate. The expanded image data is converted to picture signals of a given format which are output as the RGB image data.

> As explained above, according to the present embodipixels image data, converts them to digital image data, interpolate the digital image data, and compresses the interpolated image data at a predetermined compression rate for storage. In the output operation, the invention expands the stored image data and then outputs it, Thereby, it is possible to prevent the generation of jitter and the resultant color-stain, and thus it is possible to obtain high resolution and high quality pictures.

Also, when the interpolated image data is compressed recording medium 8, such as an IC card, it is possible to store a plurality of image data on the IC card and thus is possible to obtain a practical, broad-use apparatus.

Note that, in the present embodiment explained, wherein the imaging device required the shifting of the pixels of three sets of CCD's in the horizontal and vertical directions and the performing of a high definition signal process (interpolation process) to obtain the high 5 picture quality images. However, the present invention can be applied even to cameras with one or two sets of CCD's by shifting the pixels in just one directional, such as the horizontal direction.

Also, because the interpolated image data is com- 10 pressed directly, and the compressed image data is stored in the recording means, such as an IC card, it is possible to store a plurality of image data on a IC card and is thus possible to obtain a practical, broad-use apparatus. 15

Many widely different embodiments of the present invention may be constructed without departing from the spirit and scope of the present invention, and it should be understood that the present invention is not restricted to the specific embodiments described above. 20 What is claim is:

What is claim is:

1. An apparatus for processing an image data signal formed of at least three color components, each having an analog intensity, produced by an imaging means having first image generation elements and second 25 image generation elements arranged at the same registration positions on a two dimensional plane, said first image generation elements and said second image generation elements being spaced at a predetermined pitch in two orthogonal directions, and third image genera- 30 tion elements arranged at positions shifted by a half pitch from the registration position of said first and second image generation elements in said two orthogonal directions, comprising:

- conversion means for converting the analog intensi- 35 ties of said color components of said image data signal to digital color component data;

- compression means for compressing said digital color component data at a predetermined rate greater than 1/1, whereby when said predetermined rate is 40 1/1 said image data signal is not compressed;

- storage means for storing said compressed digital color component data on a digital recording medium;

- data reading means for reading said digital color com- 45 ponent data from said digital recording medium;

- expansion means for expanding said digital color component data read from said digital recording medium at a predetermined expansion rate, to produce expanded data substantially the same as the 50 digital color component data before compression; and

- interpolation means for interpolating at least one image data representing an intensity of an image generation element arranged between two adjacent 55 image generation elements in a first direction and between two adjacent image generation elements in a second direction, said second direction being orthogonal to said first direction, by using said expanded digital color component data represent- 60 ing the intensities of said adjacent image generation elements to thereby provide reproduced image picture data having a predetermined resolution.

2. An apparatus according to claim 1, further comprising timing adjusting means for adjusting a timing of 65 said interpolated color component data as a function of the positions of said first, second and third image generation elements.

3. An apparatus according to claim 1, further comprising picture reproduction means responsive to the interpolated image data for reproducing a picture substantially the same as an original picture.

4. An apparatus according to claim 1, wherein said compression means compresses said digital color component data as a function of the quantity of said image data.

the horizontal direction. 5. An apparatus according to claim 1, wherein said compressed directly, and the compressed image data is ored in the recording means, such as an IC card, it is

6. An apparatus according to claim 1, wherein said digital recording medium comprises a static memory.

7. An apparatus according to claim 1, wherein said digital recording medium comprises a memory card.

8. An apparatus according to claim 1, wherein said storage means and said digital recording medium are integrated as an integrated circuit card.

9. An apparatus according to claim 1, wherein said expansion means expands said digital color component data as a function of the quantity of said image data.

10. An apparatus according to claim 1, wherein said expansion means expands said digital color component data as a function of the arrangement of said image generation elements.

11. An apparatus according to claim 1, wherein said three color components comprise red, green and blue color components.

12. An apparatus according to claim 11, wherein said first image generation elements and said second image generation elements generate red image data and blue image data, respectively, and said third image generation elements generate green image data.

13. An apparatus according to claim 1, wherein said apparatus is an electronic camera.

14. An apparatus according to claim 1, wherein said apparatus is an electronic still camera for processing substantially still image data.

15. An apparatus for processing digital color component image data derived from at least three color components, each having an analog intensity, produced by an imaging means having first image generation elements and second image generation elements arranged at the same registration positions on a two dimensional plane, said first image generation elements and said second image generation elements being spaced at a predetermined pitch in two orthogonal directions, and third image generation elements arranged at positions shifted by a half pitch from the registration position of said first and second image generation elements in said two orthogonal directions, the digital color component image data being recorded in compressed form on a digital recording medium, comprising:

data reading means for reading said compressed digital color component image data from said digital recording medium;

- expansion means for expanding said digital color component image data read from said recording medium at a predetermined expansion rate, to produce expanded data substantially the same as the digital color component image data before compression; and

- interpolating means for interpolating at least one image data representing an intensity of an image generation element arranged between two adjacent image generation elements in a first direction and between two adjacent image generation elements

in a second direction, said second direction being orthogonal to said first direction, by using said expanded digital color component image data representing the intensities of said adjacent image generation elements to thereby provide reproduced 5 image picture having a predetermined resolution.

16. An apparatus according to claim 15, further comprising timing adjusting means for adjusting a timing of said interpolated color component data as a function of the positions of said first, second and third image gener- 10 ation elements.

17. An apparatus according to claim 15, further comprising picture reproduction means responsive to the interpolated data for reproducing a picture substantially the same as an original picture. 15

18. An apparatus according to claim 15, wherein said digital recording medium comprises a static memory.

19. An apparatus according to claim 15, wherein said digital recording medium comprises a memory card.

20. An apparatus according to claim 15, wherein said 20 expansion means expands said digital color component image data as a function of the quantity of said image data

21. An apparatus according to claim 15, wherein said expansion means expands said digital color component 25 image data as a function of the arrangement of said image generation elements.

22. An apparatus according to claim 15, wherein said three color components comprise red, green and blue color components.

23. An apparatus according to claim 22, wherein said first image generation elements and said second image generation elements generate red image data and blue image data, respectively, and said third image generation elements generate green image data. 35

24. An apparatus according to claim 15, wherein compression rate data representing the compression of said recorded compressed digital color component image data are recorded on and read from said digital recording medium; and

wherein said expansion means expands said digital color component image data read from said digital recording medium at an expansion rate determined by said compression rate data read from said digital recording medium.

25. An apparatus for processing an image data signal formed of at least three color components, each having an analog intensity, produced by an imaging means having first image generation elements and second image generation elements arranged at the same regis- 50 tration positions on a two dimensional plane, said first image generation elements and said second image generation elements being spaced at a predetermined pitch in two orthogonal directions, and third image generation elements arranged at positions shifted by half a 55 first image generation elements and said second image pitch from the registration position of said first and second image generation elements in said two orthogonal directions, comprising:

conversion means for converting the analog intensities of said color components of said image data 60 apparatus is an electronic camera. signal to digital color component data;

interpolation means for interpolating at least one image data representing an intensity of an image generation element arranged between two adjacent between two adjacent image generation elements in a second direction, said second direction being orthogonal to said first direction, by using said

12

digital color component data representing the intensities of said adjacent image generation elements:

- compression means for compressing said interpolated digital color component data at a predetermined rate greater than 1/1, whereby when said predetermined rate is 1/1 said image data signal is not compressed;

- storage means for storing said compressed digital color component data on a digital recording medium;

- data reading means for reading said digital color component data from said digital recording medium; and

- expansion means for expanding said digital color component data read from said digital recording medium at a predetermined expansion rate, to produce expanded data substantially the same as the digital color component data before compression.

26. An apparatus according to claim 25, further comprising timing adjusting means for adjusting a timing of said interpolated color component data as a function of the positions of said first, second and third image generation elements.

27. An apparatus according to claim 25, further comprising picture production means responsive to the expanded data for reproducing a picture substantially the same as an original picture.

28. An apparatus according to claim 25, wherein said 30 compression means compresses said digital color component data as a function of the quantity of said image data

29. An apparatus according to claim 25, wherein said compression means compresses said digital color component data as a function of the arrangement of said image generation elements.

30. An apparatus according to claim 25, wherein said digital recording medium comprises a static memory.

31. An apparatus according to claim 25, wherein said 40 digital recording medium comprises a memory card.

32. An apparatus according to claim 25, wherein said storage means and said digital recording medium are integrated as an integrated circuit card.

33. An apparatus according to claim 25, wherein said 45 expansion means expands said digital color component data as a function of the quantity of said image data.

34. An apparatus according to claim 25, wherein said expansion means expands said digital color component data as a function of the arrangement of said image generation elements.

35. An apparatus according to claim 25, wherein said three color components comprise red, green and blue color components.

36. An apparatus according to claim 35, wherein said generation elements generate red image data and blue image data, respectively, and said third image generation elements generate green image data.

37. An apparatus according to claim 25, wherein said

38. An apparatus according to claim 25, wherein said apparatus is an electronic still camera for processing substantially still image data.

39. An apparatus for processing an image data signal image generation elements in a first direction and 65 formed of at least three color components, each having an analog intensity, produced by an imaging means having first image generation elements and second image generation elements arranged at the same regisCase 8:13-cv-00546-JVS-AN Document 1 Filed 04/05/13 Page 26 of 260 Page ID #:29

tration positions on a two dimensional plane, said first image generation elements and said second image generation elements being spaced at a predetermined pitch in two orthogonal directions, and third image generation elements arranged at positions shifted by a half 5 pitch from the registration positions of said first and second image generation elements in said two orthogonal directions, comprising:

- conversion means for converting the analog intensities of said color components of said image data 10 signal to digital color component data;

- interpolating means for interpolating at least one image data representing an intensity of an image generation element arranged between two adjacent image generation elements in a first direction and 15 between two adjacent image generation elements in a second direction, said second direction being orthogonal to said first direction, by using said digital color component data representing the intensities of said adjacent image generation ele- 20 ments;

- compression means for compressing said interpolated digital color component data at a predetermined rate greater than 1/1, whereby when said predetermined rate is 1/1 said image data signal is not com- 25 pressed; and

- storage means for storing said compressed digital color component data on a digital recording medium.

**40**. An apparatus according to claim **39**, further com- 30 prising timing adjusting means for adjusting a timing of said interpolated color component data as a function of the positions of said first, second and third image generation elements.

**41**. An apparatus according to claim **39**, wherein said 35 compression means compresses said digital color component data as a function of the quantity of said image data.

42. An apparatus according to claim 39, wherein said compression means compresses said digital color com- 40 ponent data as a function of the arrangement of said image generation elements.

43. An apparatus according to claim 39, wherein said digital recording medium comprises a static memory.

44. An apparatus according to claim 39, wherein said 45 digital recording medium comprises a memory card.

45. An apparatus according to claim 39, wherein said storage means and said digital recording medium are integrated as an integrated circuit card.

**46**. An apparatus according to claim **39**, wherein said 50 nal directions, comprising the steps of: three color components comprise red, green and blue color components.

47. An apparatus according to claim 46, wherein said first image generation elements and said second image generation elements generate red image data and blue 55 image data, respectively, and said third image generation elements generate green image data.

48. A method of processing an image data signal formed of at least three color components, each having an analog intensity, produced by an imaging means 60 having first image generation elements and second image generation elements arranged at the same registration positions on a two dimensional plane, said first image generation elements and said second image generation elements being spaced at a predetermined pitch 65 in two orthogonal directions, and third image generation elements being arranged at positions shifted by a half pitch from the registration position of said first and

second image generation elements in said two orthogonal directions, comprising the steps of:

- converting the analog intensities of said color components of said image data signal to digital intensity color component data;

- compressing said digital color component data at a predetermined rate greater than 1/1, whereby when said predetermined rate is 1/1 said image data signal is not compressed;

- storing said compressed digital color component on a digital recording medium;

- reading said digital color component data from said digital recording medium;

- expanding said digital color component data read from said digital recording medium at a predetermined expansion rate, to produce expanded data substantially the same as the digital color component data before compression; and

- interpolating at least one image data representing an intensity of an image generation element arranged between two adjacent image generation elements in a first direction and between two adjacent image generation elements in a second direction, said second direction being orthogonal to said first direction, by using said expanded digital color component data representing the intensities of said adjacent image generation elements to thereby provide reproduced image picture data having a predetermined resolution.

49. A method according to claim 48, further including the step of adjusting a timing of said interpolated color component data as a function of the positions of said first, second and third image generation elements.

50. A method according to claim 48, further including the step of responding to the interpolated image data to reproduce a picture substantially the same as an original picture.

51. A method of processing an image data signal formed of at least three color components, each having an analog intensity, produced by an imaging means having first image generation elements and second image generation elements arranged at the same registration positions on a two dimensional plane, said first image generation elements and said second image generation elements being spaced at a predetermined pitch in two orthogonal directions, and third image generation elements arranged at positions shifted by a half pitch from the registration position of said first and second image generation elements in said two orthogonal directions, comprising the steps of:

- converting the analog intensities of said color components of said image data signal to digital color component data;

- interpolating at least one image data representing an intensity of an image generation element arranged between two adjacent image data generation elements in a first direction and between two adjacent image generation elements in a second direction, said second direction being orthogonal to said first direction, by using said digital color component data representing the intensities of said adjacent image generation elements;

- compressing said interpolated digital color component data at a predetermined rate greater than 1/1, whereby when said predetermined rate is 1/1 said image data signal is not compressed;

- storing said compressed digital color component data on a digital recording medium;

5,442,718

reading said digital color component data from said recording medium; and

expanding said digital color component data read from said digital recording medium at a predetermined expansion rate, to produce expanded data 5 substantially the same as the digital color component data before compression, thereby providing image picture data having a predetermined resolution. 16

52. A method according to claim 51, further including the step of adjusting a timing of said interpolated color component data as a function of the positions of first, second and third image generation elements.

53. A method according to claim 51, further including the step of responding to said image picture data to produce a picture substantially the same as an original picture.

\*

Exhibit A Page 25

\* \* \* \*

10

15

20

25

30

35

40

45

50

55

60

65

Case 8:13-cv-00546-JVS-AN Document 1 Filed 04/05/13 Page 28 of 260 Page ID #:31

# EXHIBIT B

# United States Patent [19]

#### Ueda

#### [54] METHOD AND APPARATUS FOR SERIAL TRANSMISSION AND/OR RECEPTION OF NONSYNCHRONOUS, MULTIPLEXED SIGNALS

- [75] Inventor: Mamoru Ueda, Kanagawa, Japan

- [73] Assignee: Sony Corporation, Tokyo, Japan

- [21] Appl. No.: **291,194**

- [22] Filed: Aug. 16, 1994

- [30] Foreign Application Priority Data

- Aug. 24, 1993 [JP] Japan ...... 5-231019

- [51] Int. Cl.<sup>6</sup> ...... H04N 7/52; H04N 7/54

#### [56] **References Cited**

#### **U.S. PATENT DOCUMENTS**

| 3,755,624 | 8/1973  | Sekimoto          | 348/479  |

|-----------|---------|-------------------|----------|

| 3,988,528 | 10/1976 | Yanagimachi et al | 348/481  |

| 4,542,406 |         | Shimoyama et al   | 348/484  |

| 4,544,950 | 10/1985 | Tu                | 348/485  |

| 4,706,109 | 11/1987 | Murray            | 348/481  |

| 4,851,909 | 7/1989  | Noske et al       | 348/512  |

| 5,113,242 | 5/1992  | Tsinberg et al    | 348/489  |

| 5,138,440 | 8/1992  | Radice            | . 358/13 |

| 5,199,030 | 3/1993  | Ueda              | . 370/68 |

| 5,231,492 | 7/1993  | Dangi et al       | 348/423  |

| 5,287,182 | 2/1994  | Haskell et al     | 348/484  |

|           |         |                   |          |

#### FOREIGN PATENT DOCUMENTS

0488225A2 11/1991 European Pat. Off. ........... H04J 3/06

[11] **Patent Number:** 5,523,795

### [45] **Date of Patent:** Jun. 4, 1996

0598295A1 11/1993 European Pat. Off. ......... H04N 7/13

#### OTHER PUBLICATIONS

SMPTE Journal, vol. 102, No. 10, Oct. 1993, Scarsdale, New York, U.S.A., pp. 905–909; K. Y. Reynolds, et al., "Multiplexing and Demultiplexing Digital Audio and Video in Today's Digital Environment".

4:2:2 Digital Video: Background and Implementation, 1989, SMPTE, White Plains, New York, U.S.A., pp. 77–82; K. P. Davies, "Some Concepts for the Digital Television Studio". SMPTE Journal, vol. 102, No. 2, Feb. 1993, Scarsdale, New York, U.S.A., pp. 174–179; "Proposed SMPTE Standard 259M".

Signal Processing Image Communication, vol. 4, No. 2, May 1992, pp. 153–159; A. G MacInnis, "the MPG System Coding Specification".

Primary Examiner—Safet Metjahic Attorney, Agent, or Firm—Limbach & Limbach

#### [57] ABSTRACT

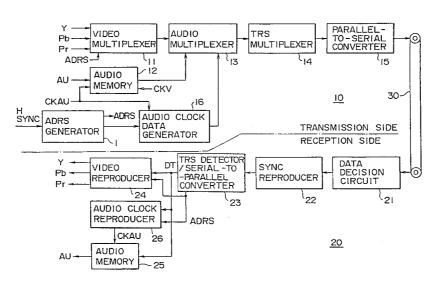

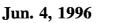

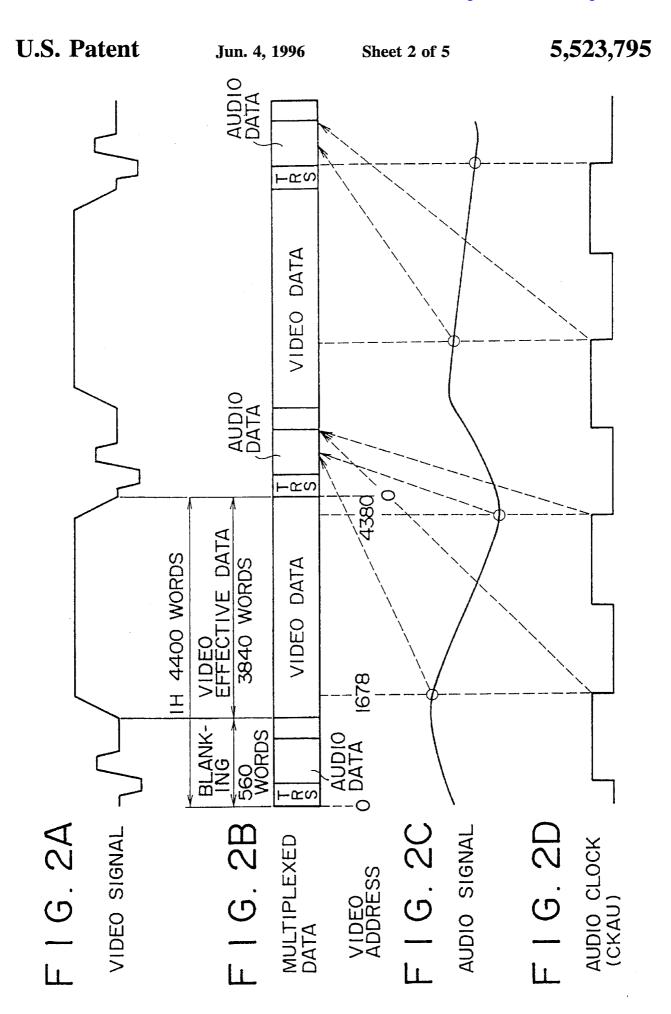

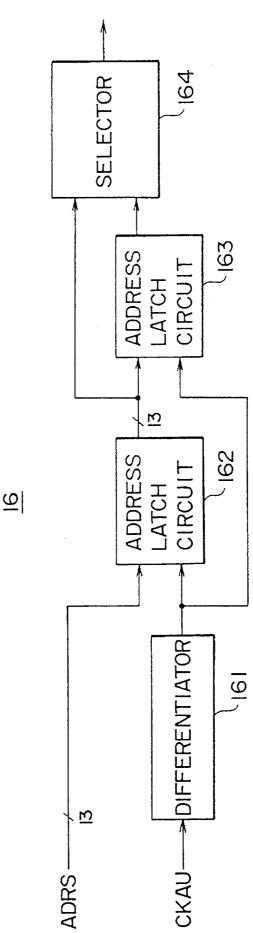

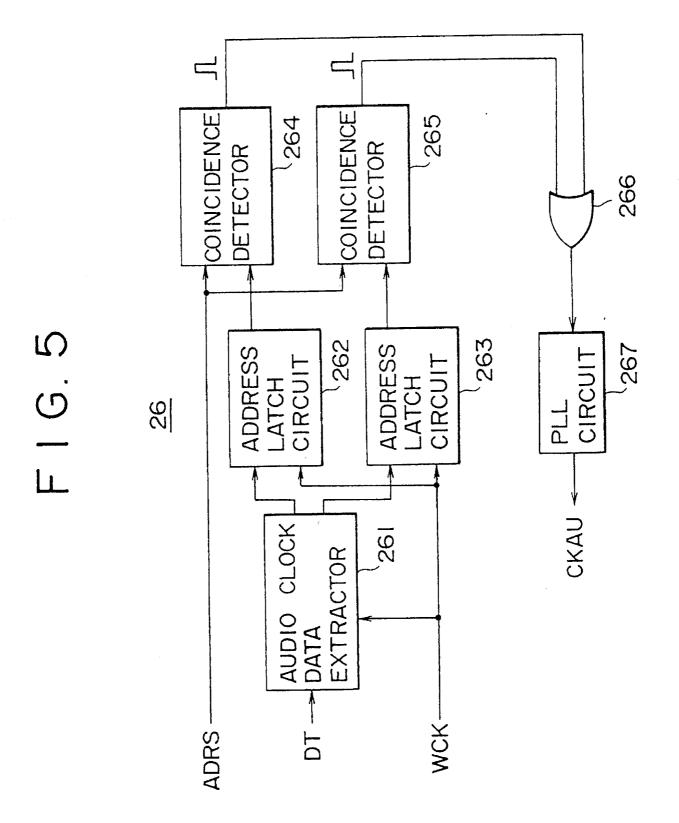

A method and an apparatus capable of transmitting and receiving multiplexed signals as serial data in such a manner that, even in a state where a continuous signal such as an audio digital signal is not in synchronism with another signal such as a video digital signal, the continuous signal can be properly reproduced on a reception side. Address data based on a word clock of another digital signal is sampled on a transmission side in accordance with a sampling clock of the continuous signal, and the sampled address value is included in the multiplexed signals to be thereby transmitted together to the reception side. Then on the reception side, a word clock synchronously locked to the word clock of the transmission-side another digital signal is reproduced from the received serial data, and address data is generated on the basis of the reproduced word clock, so that the receptionside clock of the continuous signal is reproduced from the generated address data and the transmitted address value included in the multiplexed signals, whereby the continuous signal is reproduced in accordance with the clock thus reproduced.

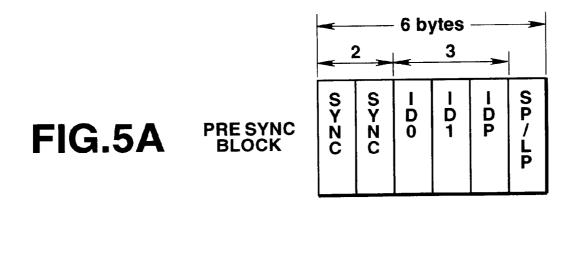

#### 11 Claims, 5 Drawing Sheets

Sheet 1 of 5

**U.S. Patent**

Jun. 4, 1996 She

Sheet 3 of 5

Exhibit B Page 29

**U.S. Patent**

Jun. 4, 1996

F I G. 4

Jun. 4, 1996

Sheet 5 of 5

5,523,795

5,523,795

5

#### METHOD AND APPARATUS FOR SERIAL TRANSMISSION AND/OR RECEPTION OF NONSYNCHRONOUS, MULTIPLEXED SIGNALS

#### BACKGROUND OF THE INVENTION

The present invention relates to a method and an apparatus for multiplexing, for example, a digital audio signal with a digital video signal by time division and transmitting and/or receiving such multiplexed signals as serial data, and more particularly, to a method and an apparatus capable of transmitting and/or receiving multiplexed signals even in a state where an audio signal is not synchronized with a video signal.

For transmission of a digital video signal, there is known an exemplary system employing a serial digital interface. According to this interface, a digital video signal is transmitted as 1-bit serial data. More specifically, there is proposed in the serial digital interface a technique in which a blanking period of the video signal is rendered vacant due to non-transmission of horizontal and vertical sync signals, and a digital audio signal is transmitted during such blanking period through time-base compression and multiplexing.

In U.S. Pat. No. 5,199,030, there is disclosed a method of  $_{25}$  multiplexing and transmitting a digital video signal and a digital audio signal.

The serial digital interface mentioned above has the merit that both a digital video signal and a digital audio signal can be transmitted via a single coaxial cable without signal 30 deterioration, whereby the signal connection between various digital video apparatus can be remarkably simplified.

Generally, the sampling clock frequencies for the digital video signal and the digital audio signal are different from each other. For example, the sampling rate in the case of <sup>35</sup> NTSC video signal is 14.3 MHz, whereas the rate for the audio signal is 48 kHz. The transmission clock rate for the audio signal is generally set to be equal to that for the digital video signal. Assuming in the above example that each sample is composed of 10 bits, it follows that the transmission rate is 143 Mbps. The audio data is compressed in its time base and is multiplexed to form data of the above transmission rate.