圖、小晶片互聯標準UCIe3.0將連線頻寬提升至64GT/s

隨着雲端運算、高效能計算(HPC)以及人工智慧(AI)等領域的蓬勃發展,對於半導體設計的需求也日益嚴苛。傳統上,單晶片設計(monolithic chip design)面臨著製造成本不斷攀升和技術挑戰日益增加的困境。為應對這些挑戰,小晶片(Chiplet)架構應運而生,成為半導體產業轉型的關鍵趨勢。

小晶片是一種模組化的積體電路單元,它將不同功能的電路區塊(例如 CPU、GPU、記憶體控制器或 I/O 介面)設計成更小、可重複使用的獨立晶片。這些小晶片可以在單一封裝中靈活地組合在一起,形成一個完整的系統級封裝(System-in-Package, SiP)。小晶片模組化的設計提升晶片設計的效率、靈活性和客製化能力,同時有效降低了開發成本和時間。

然而,在UCIe聯盟成立之前,大多數基於小晶片的半導體產品仍然依賴各廠商專有的互連技術進行連接。然而,缺乏標準化限制了不同廠商之間小晶片的互通性,阻礙了小晶片的發展。

通用晶片互連介面(Universal Chiplet Interconnect Express,簡稱 UCIe)聯盟正是在此背景下於 2022年 成立。由半導體業界的領導者,包括AMD、Arm、Google Cloud、Intel、Meta、微軟、NVIDIA、Qualcomm、三星(Samsung Electronics)、台積電(TSMC)和日月光(ASE)等晶片製造商與超大規模雲端服務供應商共同推動。UCIe聯盟的目標是制定一套開放、標準化的互連規範,使來自不同廠商、採用不同晶圓廠製程、具備不同功能的小晶片都能在單一封裝中協同工作,促進晶片設計從傳統單一晶片邁向模組化、小晶片化的技術演進,以建立一個開放的晶片間互連生態系統。UCIe 1.0規範於2022年首次發布,為開放式小晶片互連奠定了基礎。

為了持續滿足市場對高效能運算、人工智慧等應用不斷增長的頻寬需求,UCIe 聯盟於2025年8月5日正式發布了UCIe 3.0規範。此次發布是UCIe標準演進的一個重要里程碑,它在UCIe 2.0的基礎上,帶來了顯著的性能提升和多項架構更新。

UCIe 2.0與UCIe 3.0的差異與關鍵突破

UCIe 3.0規範與一年前發布的 UCIe 2.0 相比,其頻寬上限由 32 GT/s 提升至 48 GT/s 和 64 GT/s,其中GT/s 是指每秒百萬次傳輸(Giga Transfers per second),是一個描述物理層信號傳輸能力的單位,表示每秒傳輸的次數,而不是實際的有效資料量。

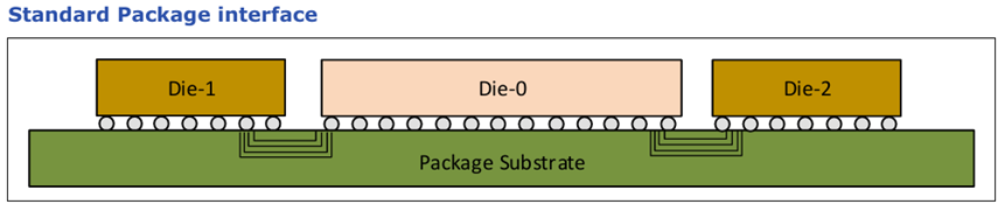

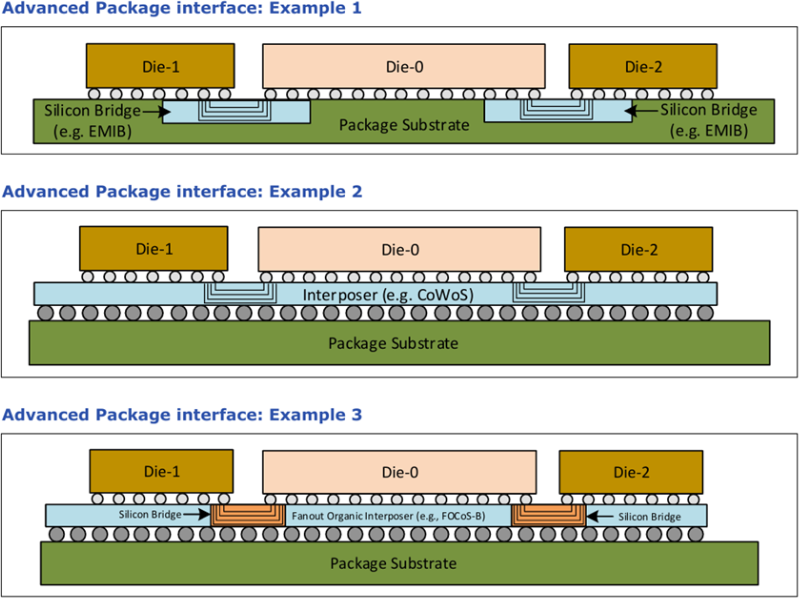

UCIe 3.0標準主要提升了UCIe-S(2D標準封裝)和UCIe-A(2.5D先進封裝)設計的傳輸能力。

圖1 標準封裝介面 (圖片來源:UCIe 3.0 Specification)

圖2 先進封裝介面 (圖片來源:UCIe 3.0 Specification)

提升小晶片間的傳輸能力,有助於支援AI、HPC和數據分析等領域對高速傳輸的需求。UCIe聯盟主席指出,晶片尺寸不會因頻寬增加而改變,因此需在有限互連邊界內提升頻寬密度。而且,UCIe 3.0維持了向後兼容性,確保現有系統和基礎設施能夠無縫整合新標準至關重要。

UCIe 3.0 的其他增強功能

除了頻寬和向下兼容性,UCIe 3.0還引入了多項架構和功能上的強化設計,以提高系統的效率、彈性和可靠性:

- 執行時重新校準(Runtime Recalibration)

- 可擴展的邊緣頻寬(Extended Reach Sideband)

- 連續傳輸協議支持(Continuous Transmission Protocol Support)

- 標準化早期韌體下載(Early Firmware Download)

- 優先邊帶封包(Priority Sideband Packets)

- 快速節流(Fast Throttle)與緊急關機(Emergency Shutdown)機制

--------------------------------------------------------------------------------------------------------------------------------------------