圖、 非專利實施個體Vervain依據均等論,主張群聯電子侵害快閃記憶體控制器相關專利

如表一整理,於2024年3月7日,非專利實施個體 (Non-Practicing Entity, NPE), Vervain公司向美國西德州聯邦地方法院遞狀提起訴訟,主張群聯電子(Phison Electronics) 進口到美國境內銷售的快閃記憶體 (flash memory) 相關產品,侵害其所擁有的八件快閃記憶體相關專利。訴狀列出的被控侵權的SSD 和快閃記憶體控制器型號為:PS5026-E26 (消費級 SSD)、SA50 (企業級 SSD)、PS8131 (SD)、PS2251-11 (USB) 和 PS8229 (嵌入式快閃記憶體)。

這八件專利或其中部分項目,也曾被Vervain運用在其他侵權訴訟中,其他訴訟的被告包含:美光科技(Micron Technology),西方數位(Western Digital),金士頓數位(Kingston Digital),和SK海力士(SK Hynix);其中Vervain控告美光與西方數位的兩件相關訴訟已經結束。

表一、Vervain於西德州法院控告群聯電子侵害快閃記憶體控制器相關專利訴訟

| 訴訟案號 |

提起日 |

法院 |

原告 |

被告 |

訴訟專利 |

| 1:24-cv-00259 |

2024/3/7 |

Texas Western District Court |

Vervain LLC |

Phison Electronics Corp |

8891298

9196385

9997240

10950300

11830546

11854612

11967369

11967370 |

訴訟專利US8891298B的專利範圍與原告主張的侵權比對

為代表性說明Vervain公司訴訟專利的權利範圍,筆者就依據八件訴訟專利中最早申請的US8891298B專利加以說明其專利範圍,及已知的Vervain專利侵權比對論點。

表二、US8891298B2 claim 1 原文與對應翻譯

| US8891298B2 claim 1 |

US8891298B2 claim 1 翻譯 |

| 1. A system for storing data comprising: |

1. 一種資料儲存系統,包括: |

| at least one MLC non-volatile memory module comprising a plurality of individually erasable blocks; |

至少一個MLC (multi-level-cell) 非揮發性儲存模組,該模組包含多個可單獨擦除的區塊; |

| at least one SLC non-volatile memory module comprising a plurality of individually erasable blocks; and |

至少一個SLC (single-level-cel) 非揮發性儲存模組,該模組包含多個可單獨擦除的區塊;以及 |

| a controller coupled to the at least one MLC non-volatile memory module and the at least one SLC non-volatile memory module wherein the controller is adapted to: |

一種控制器,該控制器與至少一個MLC非揮發性存儲模組和至少一個SLC非揮發性存儲模組耦合,其中該控制器適用於: |

| a) maintain an address map of at least one of the MLC and SLC non-volatile memory modules, the address map comprising a list of logical address ranges accessible by a computer system, the list of logical address ranges having a minimum quanta of addresses, wherein each entry in the list of logical address ranges maps to a similar range of physical addresses within either the at least one SLC non-volatile memory module or within the at least one MLC non-volatile memory module; |

a) 維護至少一個MLC和SLC非揮發性存儲模組的地址映射,該地址映射包括計算機系統可訪問的邏輯地址範圍列表,該邏輯地址範圍列表具有最小地址量 (claim3 進一步限定該最小地址量為一頁page),其中邏輯地址範圍列表中的每個條目映射到至少一個SLC非揮發性存儲模組或至少一個MLC非揮發性存儲模組中的類似物理地址範圍; |

| b) determine if a range of addresses listed by an entry and mapped to a similar range of physical addresses within the at least one MLC non-volatile memory module, fails a data integrity test, and, in the event of such a failure, the controller remaps the entry to the next available equivalent range of physical addresses within the at least one SLC non-volatile memory module; |

b) 確定條目列出的位址範圍(對應到至少一個MLC非揮發性儲存模組中的類似實體位址範圍)是否未能通過資料完整性測試,如果未能通過,則控制器將該條目重新對應到至少一個SLC非揮發性儲存模組中的下一個可用等效實體位址範圍; |

| c) determine which of the blocks of the plurality of the blocks in the MLC and SLC non-volatile memory modules are accessed most frequently by maintaining a count of the number of times each one of the blocks is accessed; and |

c) 透過統計每個區塊被存取的次數,確定MLC和SLC非揮發性儲存模組中的多個區塊中哪些區塊被存取的頻率最高; |

| d) allocate those blocks that receive the most frequent writes by transferring the respective contents of those blocks to the at least one SLC non-volatile memory module. |

d) 將寫入次數最多的區塊的內容傳送到至少一個SLC非揮發性儲存模組,從而分配這些區塊。 |

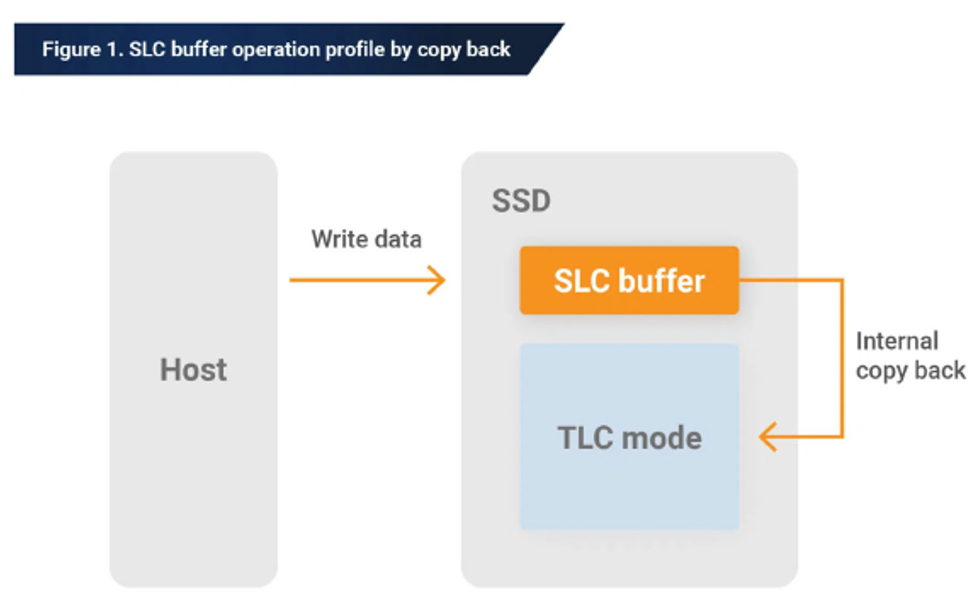

如圖一所示,針對 "控制器a)步驟:維護至少一個MLC和SLC非揮發性存儲模組的地址映射... ": 於訴狀第67段,Vervain將該元件對應到下列群聯電子技術文件,以說明被控的群聯電子控制器,可控制的固態硬碟內包含MLC ( "TLC模式", 3-bit per cell) 記憶體和 SLC (Single Level Cell) 緩衝區。

圖一、訴狀第67段部分截圖

如圖二所示,針對 "控制器b)步驟:確定條目列出的位址範圍 ... 是否未能通過資料完整性測試,如果未能通過,則控制器將該條目重新對應到...下一個可用等效實體位址範圍... ",於訴狀第75~76段,Vervain將該元件對應到下列群聯電子的SmartRefresh相關的技術文件,以說明群聯被控產品會掃描記憶體的區塊錯誤位元數,當發現錯誤位元數超過閾值的較高風險區塊時,會採取措施來維持資料完整性 (圖示紅色的資料區塊D5似乎是重新對應到未用區塊S0)。

針對最後兩個控制器步驟:"c) 透過統計每個區塊被存取的次數,確定MLC和SLC非揮發性儲存模組中的多個區塊中那些區塊被存取的頻率最高;d) 將寫入次數最多的區塊的內容傳送到至少一個 SLC 非揮發性儲存模組,從而分配這些區塊。”

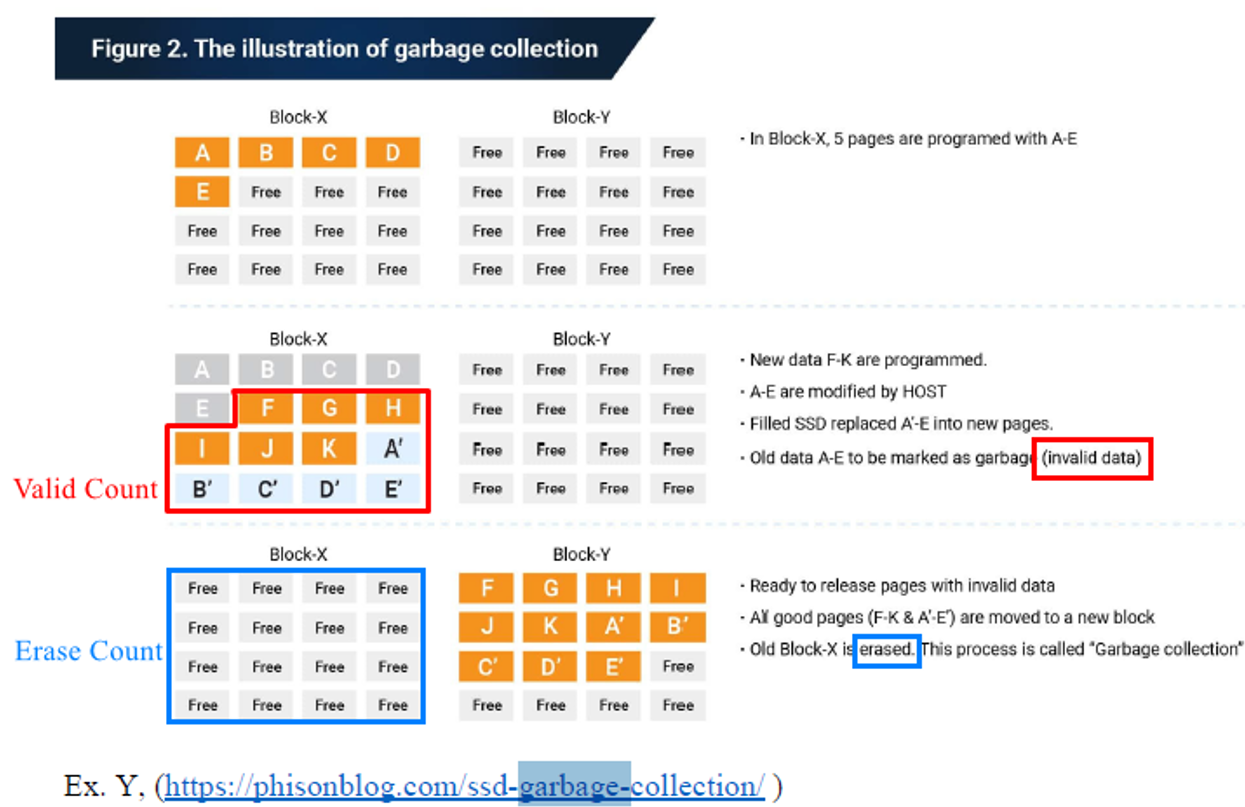

參考群聯電子提出的 "#110駁回未及時披露證據和侵權理論的訴訟動議 _MOTION to Strike UNTIMELY DISCLOSURE OF EVIDENCE AND INFRINGEMENT THEORIES" 內容,Vervain專家證人似乎企圖依據均等論 (Doctrine of Equivaent, DOE),將 ”被存取的頻率最高” 和 “寫入次數最多的區塊” 兩個元件均等對應到群聯電子產品的 “有效區塊數Valid Count” 和 “刪除次數Erase Count”。

如圖三所示,於訴狀第138段,Vervain揭露群聯電子產品實施 "垃圾收集Garbage Collection" 操作的相關技術文件描述:在同一個NAND快取記憶體區塊Block-X中持續寫入/修改資料後,則該Block-X區塊可能對應產生A~E無效資料Invalid Data。為了要消除A~E無效資料占用區域,需將A’~E’, F~K等有效資料先複製搬移到Block-Y,然後將快閃記憶體Block-X整個 “區塊刪除Blocked Erased”,如此將A~E無效資料占用區域回復為可再寫入資料的可用Free記憶單元。

筆者嘗試將 有效區塊數Valid Count 和 刪除次數Erase Count 註記於圖四中;而Vervain專利證人似乎主張 "較低的有效區塊數" 或是 "較高的刪除次數",均等於專利範圍所描述的確定 "存取頻率最高” 或 "寫入次數最多” 的損耗程度較高,資料錯誤風險較高區塊;因此Block-X區塊可能稍後會被寫入SLC緩衝區中。

圖三、訴狀第138段部分截圖

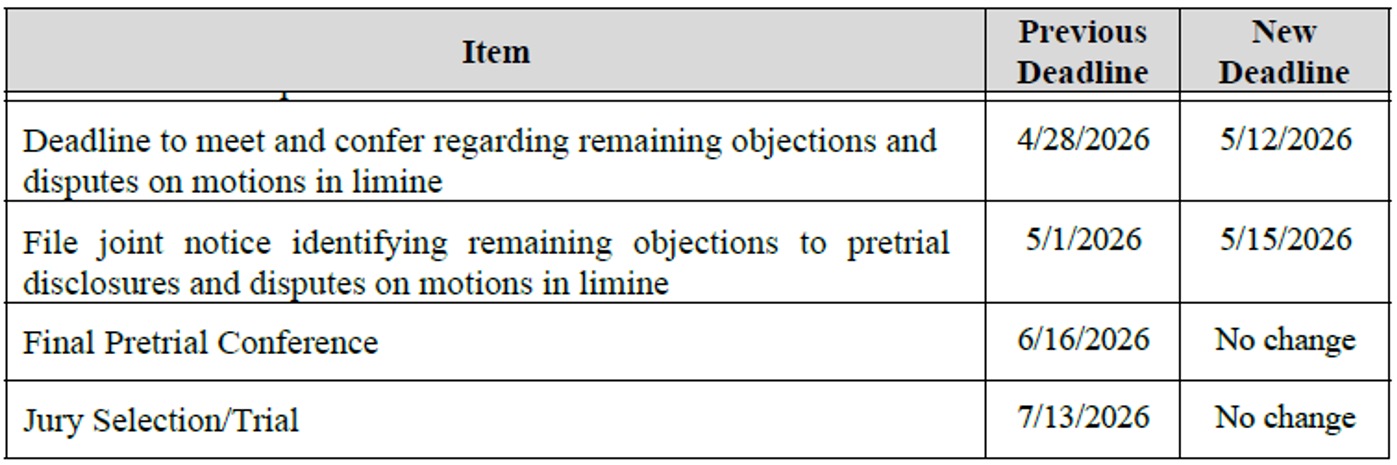

如圖四所示,原本排定2026年7月13日選擇陪審團成員後進行陪審團審判;但法院於1月26日發出修正時程命令,取消上述開庭日。依據先前程序延後約半個月,故筆者評估延遲調整後的陪審團審判日期應該不會晚於今年年底。

圖四、法院2026 Jan. 26發出的訴訟時程命令部分截圖

針對被控產品的 有效區塊數Valid Count 和 刪除次數Erase Count 是如何地等同於專利範圍的 存取頻率最高accessed most frequently 或 寫入次數最多receive the most frequent writes,可預期雙方律師稍後會有一番激烈攻防。(2448字;圖1)

參考資料:

Vervain Sues SK hynix, Trials in Its Existing Suits Set for Summer, Feb. 9, 2026, RPX Empower.

Vervain, LLC v. Phison Electronics Corporation (1:24-cv-00259), Court Listener

--------------------------------------------------------------------------------------------------------------------------------------------